# 2<sup>nd</sup> International Workshop on Analysis Tools and Methodologies for Embedded and Real-time Systems (WATERS 2011)

July 5th, 2011, Porto, Portugal

In conjunction with the  $23^{rd}$  Euromicro Conference on Real-Time Systems (ECRTS 2011)

# Table of Contents

| Message from the Program Chairs<br>Program Committee                                                                                                                     | $\frac{3}{5}$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Research Papers                                                                                                                                                          |               |

| SMFF: System Models for Free<br>Moritz Neukirchner, Steffen Stein and Rolf Ernst                                                                                         | 6             |

| On the Gap between Schedulability Tests and Automotive Task Model<br>Saoussen Anssi, Stefan Kuntz, Sébastien Gérard and François Terrier                                 | 12            |

| FORTAS : Framework fOr Real-Time Analysis and Simulation<br>Pierre Courbin and Laurent George                                                                            | 21            |

| Hardware-Assisted Energy Consumption Evaluation Tool<br>for Multi-core Embedded Systems<br>Shiao-Li Tsao, Jyun-Wei Lin, QuanChung Chen and Chen-Wei Huang                | 27            |

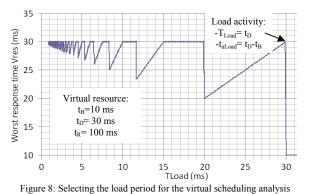

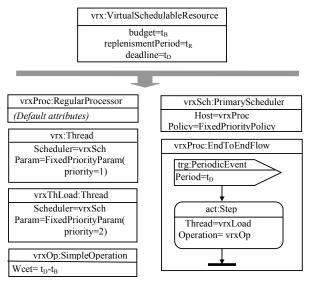

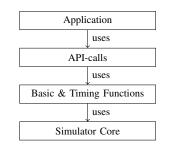

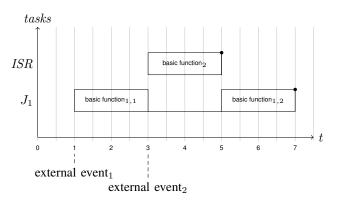

| Modelling real-time applications based on resource reservations<br>Laura Barros, César Cuevas, Patricia López Martínez, José María Drake<br>and Michael González Harbour | 33            |

| SimTrOS: A Heterogenous Abstraction Level Simulator<br>for Multicore Synchronization in Real-Time Systems<br>Jörn Schneider, Michael Bohn and Christian Eltges           | 39            |

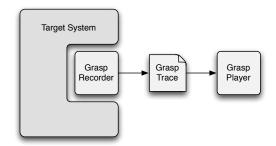

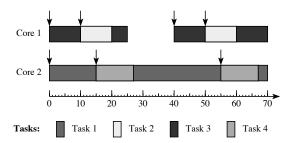

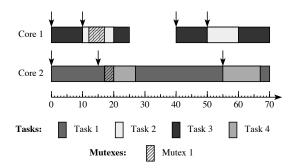

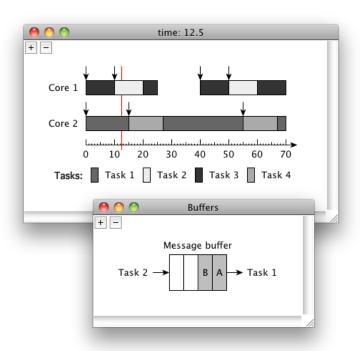

| Grasp: Visualizing the Behavior of Hierarchical Multiprocessor<br>Real-Time Systems<br>Mike Holenderski, Reinder Bril and Johan Lukkien                                  | 45            |

| Modeling Real-Time Networks with MAST2<br>Michael González Harbour, J. Javier Gutiérrez, J. María Drake, Patricia López<br>and J. Carlos Palencia                        | 51            |

| Continuous Constant-Memory Monitoring of Embedded Software Timing<br>Johan Kraft and Thomas Nolte                                                                        | 57            |

# Message from the Program Chairs

Research in real-time systems has gone very far from the initial seminal papers back in the 70s. Many algorithms, design methodologies, techniques and tools have been proposed, spanning several application areas, from RTOS to distributed systems, from safety critical to soft real-time systems. However, unlike other research areas (e.g., networking) there are no widely recognized reference tools or methodologies for comparing different research works in the area.

In fact, the comparison among results achieved by different research groups becomes non-trivial or impossible due to the lack of common tools or methodologies by means of which the comparison is done. For example, different authors use different algorithms for generating random task sets, different application traces when simulating dynamic real-time systems, different simulation engines when simulating scheduling algorithms. Therefore, research in the field of real-time and embedded systems would greatly benefit from the availability of well-engineered, possibly open tools, simulation frameworks and data sets which may constitute a common metrics for evaluating simulation or experimental results in the area. Also, it would be nice to have a possibly wide set of reusable data sets or behavioural models coming from realistic industrial use-cases over which to evaluate the performance of novel algorithms. Availability of such items would increase the possibility to compare novel techniques in dealing with problems already tackled by others from the multifaceted viewpoints of effectiveness, overhead, performance, applicability, etc.

The ambitious goal of the International Workshop on Anaysis Tools and Methodologies for Embedded and Real-time Systems is to start creating a common ground and a community to collect methodologies, software tools, best practices, data sets, application models, benchmarks and any other way to improve comparability of results in the current practice of research in realtime and embedded systems. People from industry are welcome to contribute as well with realistic data or methods coming from their own experience.

The workshop seeks original contributions on methods and tools for realtime and embedded systems analysis, simulation, modelling and benchmarking. We look for papers describing well-engineered, highly reusable, possibly open, tools that can be used by other researchers.

Areas of interest include, but are not limited to:

- Simulation of real-time, distributed and embedded systems

- Simulation of multi-core, many-core and massively parallel and distributed systems

- Modeling, analysis and simulation of Operating Systems components

- Tools and methodologies for real-time analysis

- Instrumentation of Operating Systems

- Tracing methods and overhead analysis

- Power consumption models and experimental data for real-time poweraware systems

- Middleware components and mechanisms for distributed infrastructures supporting real-time and QoS-aware Cloud Computing applications

- Realistic case studies and reusable data sets

- Comparative evaluation of existing algorithms

We would like to thank the Euromicro organization for having allowed us to organize this event, and particularly Gerhard Fohler for his prompt and ready support. We would like to thank all the authors for having submitted their work to the workshop for selection, the Program Committee members for their effort in reviewing the papers, the presenters for ensuring interesting sessions, and the attendees for participating into this event. We hope that interesting ideas and discussions will come out of the presentations, demos and the questions that will alternate along the day. We hope you will find this day interesting and enjoyable.

> The WATERS 2011 Chairs Giuseppe Lipari and Tommaso Cucinotta

Real-Time Systems Laboratory Scuola Superiore Sant'Anna, Pisa (Italy) {g.lipari, t.cucinotta} © sssup.it

# Program Committee

- Andrea Acquaviva (Politecnico di Torino, Italy)

- Mark Bartlett (University of York, UK)

- Ian Broster (Rapita Systems Ltd, York, UK)

- Roberto Bucher (SUPSI, Manno, Switzerland)

- Gerhard Fohler (Technische Universitaet of Kaiserslautern, Germany)

- Christopher D. Gill (Washington University, St. Louis, Missouri)

- Michael Gonzalez (Universidad de Cantabria, Spain)

- Lucia Lo Bello (University of Catania, Italy)

- Damir Isovic (Mälardalen University, Sweden)

- Julio Medina (Universidad de Cantabria, Spain)

- Thomas Nolte (Mälardalen University, Sweden)

- Luigi Palopoli (University of Trento, Italy)

- Rodrigo Santos (Universidad Nacional del Sur, Bahia Blanca, Argentina)

- Simon Schliecker (Symtavision GmbH, Braunschweig, Germany)

- Douglas C. Schmidt (Vanderbilt University, Nashville, TN)

- Marisol Garcia Valls (Universidad Carlos III de Madrid, Spain)

- Zlatko Zlatev (IT-Innovation Center, Southampton, UK)

# SMFF: System Models for Free

Moritz Neukirchner, Steffen Stein and Rolf Ernst Technische Universität Braunschweig Braunschweig, Germany neukirchner|stein|ernst@ida.ing.tu-bs.de

*Abstract*—Evaluation of scheduling, allocation or performance verification algorithms requires either analytical performance estimations or a large number of testcases. In many cases, e.g. if heuristics are employed, extensive sets of testcase systems are imperative. Oftentimes realistic models of such systems are not available to the developer in large numbers.

We present SMFF (System Models for Free) - a framework for pseudorandom generation of models of real-time systems. The generated system models can be used for evaluation of scheduling, allocation or performance verification algorithms. As requirements for the generated systems are domain-specific the framework is implemented in a modular way, such that the model is extendible and each step of the model generation can be exchanged by a custom implementation.

#### I. INTRODUCTION

During the development of e.g. scheduling or allocation algorithms or algorithms for performance verification, testcase systems are required to evaluate the applicability and performance. If formal proofs of correctness or analytically derived performance estimations can be given a small set of such systems is sufficient. However, in many cases this is not possible e.g. if heuristics are employed. In this case the algorithm has to be tested with an extensive set of testcases. For many algorithm developers, especially in academia, system models are not available in large numbers. Manually creating such system models is very time-consuming and might not respect requirements on randomness.

In this paper we address this issue and present SMFF a framework for parameter-driven generation of models of distributed real-time systems. These models incorporate a description of the platform, of the software applications mapped onto the platform and the associated scheduling and timing parameters, thus covering the entire model specification.

As system models, that are used for algorithm evaluation, have to resemble real-world systems, requirements on testcase systems may be highly domain- and problem-specific. The presented framework provides a high degree of modularity, allowing the user to extend the system-model and to replace algorithms for system model generation, thus making the framework a universal tool for testcase generation. It is available as open source software from [1]. The algorithms presented in this paper and provided along with SMFF are example implementations and were developed for the evaluation of an algorithm to find execution priorities in static-prioritypreemptively scheduled systems under consideration of timing constraints [2].

The key features of the SMFF framework are:

• Parameter-driven generation of complete system models for use as testcases

- A modular framework architecture to allow exchange of generation algorithms

- Extendible data structures to allow customization of the system model

The SMFF framework is no simulation or benchmarking environment. Thus, we do not address the issues of simulation or performance monitoring. We rather provide models as input for such tools.

This paper is structured as follows. First we will discuss how the process of system model generation can be structured into discrete steps. We will then give an overview of related work and how previous approaches relate to this structure. In section IV we will define the main terms and the system model used throughout the paper. The following sections will address the single steps of the model generation and the implemented algorithms. Section IX covers aspects of the implementation of the framework and its modularity. In section X we will present an example of system model generation with the SMFF framework. Then we will conclude the paper.

#### II. GENERAL APPROACH

In this section we will outline the general approach to generate system models of distributed real-time systems.

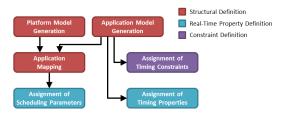

We propose to divide the process of model generation into six steps as depicted in fig. 1. The six steps can be grouped into the categories *structural definition*, *real-time property definition* and *constraint definition*. While some steps can be executed independent of each other, some require other steps to be performed beforehand (indicated by arrows).

The structural definition is composed of the *platform model* generation, the application model generation and the application mapping. During platform model generation the architecture graph is constructed. Thus this step defines the topology of the platform. In the application model generation step, application graphs are created defining the logical structure of software applications. The final step of the structural definition maps the application models onto the platform model, defining the distribution of the application on the hardware platform. Naturally this step can only be performed after architecture and application models have been created.

Real-time property definition is composed of the steps of *assignment of timing properties* and of *assignment of scheduling parameters*. In the first step tasks and communication between tasks are assigned an execution model such as best-case execution and worst-case execution times. Furthermore tasks can be assigned an activation model (e.g. activation period and activation jitter). Thus this step defines the timing of each entity of an application in isolation. This step can only be

Fig. 1: General testcase generation flow

performed after the application models have been generated. In the second step scheduling parameters, such as execution priorities for static priority preemptively (SPP) scheduled resources, are assigned to the tasks and communication. This step can only be executed after the application mapping, as scheduling parameters depend on the scheduling strategy of the resources tasks and communication have been mapped to. After these two steps the timing behavior of the system is completely specified.

The last category is composed of only one step - the *assignment of timing constraints*. In assignment of timing constraints limitations on e.g. end-to-end path latencies or output jitters can be defined. Also this step can only be performed after the application model has been created, as constraints are specified for entities of an application.

Except for the outlined dependencies the steps of the system model generation can be performed in arbitrary order and independent of each other. This gives great flexibility to the developer as it is possible to e.g. load manually defined platform models and only perform the remaining steps of the testcase generation with the provided platform model. Also the developer may introduce further dependencies to tailor the testcase generation process for his specific needs. E.g. one may make the assignment of timing properties depend on the application mapping to include processor-specific execution times.

## III. RELATED WORK

We now review previous approaches to generation of testcase system models and highlight how these approaches relate to the structure of testcase generation as described above.

For evaluation of real-time algorithms (e.g. scheduling, allocation or performance verification) many developers rely on handcrafted example systems, to highlight strengths and shortcomings of different approaches (e.g. [3], [4], [5]). Others rely on benchmark models of real applications such as MPEG2 decoders (e.g. [6]) or on more comprehensive benchmark suites as e.g. [7]. A third approach many developers take for evaluation and comparison of their algorithms is parameter-driven testcase generation (e.g. [8], [9]).

If any of the first two approaches is taken, the results of an algorithm evaluation tend to be fairly well reproducible as the set of system models is well specified and oftentimes publicly available. However the number of testcases typically is low. As a result statements about average performance of an algorithm may be inaccurate, as the examples might not be representative of the targeted domain of application or might not cover common corner-cases properly. This may bias the evaluation of an algorithm. The approach of pseudorandom parameter-driven testcase generation can provide more accurate results on average performance, as an algorithm can easily be evaluated against a large set of system models. Many developers use custom algorithms to generate testcases. Common approaches are to select a platform and application model manually and to assign timing properties in specified bounds (e.g. [9]) or to use a fixed platform and generate task sets (i.e. application models) automatically (e.g. [8], [10]). In both cases common cornercases, that might only occur for e.g. certain platforms, might be neglected. To the best of our knowledge there exists no single approach that addresses all steps of parameter-driven pseudorandom system model generation. Instead parts of the generation process have been addressed.

A fairly comprehensive tool for automatic testcase generation is task-graphs for free (TGFF) [11]. TGFF generates task graphs based on a parameter set that allows detailed influence on the topology. Furthermore it allows to generate timing properties for all tasks (periods and execution times) and latency constraints on paths. Thus it addresses the three steps of application model generation, assignment of timing properties and assignment of timing constraints. TGFF has been widely used for generation of task sets (e.g. [12], [13], [14]). However, if the algorithm under evaluation targets distributed systems with communicating tasks, platform topology and application mapping may be relevant. TGFF is not able to perform these steps of model generation, though.

The steps of application model generation and assignment of timing properties have also been studied thoroughly in the scope of single and multi-processor schedulability analysis. Here benchmarking includes generation of task sets and assignment of timing parameters such as execution times and activation periods. In many cases timing parameters of fixedsize task sets are assigned so that a specific processor load is accomplished by randomly assigning activation periods and setting the execution times to match the required utilization (see e.g. [15], [9]). [16] gives an analysis of properties of commonly used algorithms to accomplish this task and discusses their respective properties with respect to the task set parameters generated. It shows that the chosen algorithm can bias the benchmark favoring one schedulability test or the other and proposes new algorithms for timing parameter generation that have been widely adopted in the community [17], [18], [19]. These findings should be considered when designing an algorithm for timing parameter generation in the described flow of pseudorandom system generation.

We are not aware of any tool capable of generating complete system models covering the entire testcase generation flow. With the SMFF framework we aim to incorporate all steps of the testcase generation into a single framework, allowing developers to generate complete system models to evaluate their algorithms. In the following we will first provide a detailed description of the system model and then address the single steps of the testcase generation flow.

#### IV. SYSTEM MODEL

In this section, we will briefly introduce the main terms used throughout the paper and elaborate on the system model.

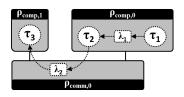

Fig. 2: System Model

The term *platform* refers to the hardware software will run on. We assume that a platform consists of set of processors (*computational resources*) interconnected by a set of communication media (*communication resources*). A platform is modeled as a bipartite graph with the two types of resources being the two types of vertices. The undirected edges between the vertices denote connectivity between two resources.

Applications are running on the platform. An application consists of a set of tasks and a set of communication channels (task links). By a task link we understand a communication entity that may be established/scheduled on a processor or communication medium. An application is modeled as a directed bipartite graph with the tasks and task links being the two types of vertices. Edges denote communication of a task via a task link while information flows in the direction of the edge. All task links have an in-degree and out-degree of 1. This model slightly deviates from the common model of task graphs, where tasks are modeled as vertices and communication between tasks as edges. We chose to modify this model to provide better expressiveness for mappings of task links. Regular task graphs can be transformed to the modified model by replacing edges by a task link vertex and two edges. We call two tasks adjacent to each other if a task link exists that is adjacent to both tasks. This notion of adjacency is identical to adjacency of tasks in regular task graphs.

Tasks are mapped on resources, signifying that a task is executed on that resource. Task links can be mapped on a computational or a communication resource indicating that communication is established via/on this resource.

An example system is depicted in fig. 2. It is composed of a platform of two computational and one communication resource ( $\rho_{comp,0}$ ,  $\rho_{comp,1}$  and  $\rho_{comm,0}$ , respectively) and one application of three tasks ( $\tau_1$ - $\tau_3$ ) that communicate over two task links ( $\lambda_1$ ,  $\lambda_2$ ). Task link  $\lambda_1$  is mapped on a computational resource, while  $\lambda_2$  is mapped on the communication resource.

As we are dealing with real-time systems timing properties can be defined. A task can be assigned an activation model and an execution model. An activation model may be a specification of e.g. an activation period and an activation jitter. An execution model can be specified by e.g. best-case and worst-case execution time (BCET and WCET). An execution model is also assigned to task links that are mapped on a communication medium. In addition to the timing properties a set of constraints on timing properties can be provided, e.g. constraints on end-to-end path latency.

In the following sections we will explain the single steps of system model generation. We will present possible characterizations for the system models and present exemplary algorithms for each step.

#### Algorithm 1 Platform Generation

- INPUT: numRes, CRes%

- 1: numCRes = value from Binomial Distribution(n=numRes, p=CRes%)

- 2: for i = 1 to i =numCRes-1 do

3: connect comm. resources i 1 and i to random comp. resource

- 4: for all unconnected comp. resources do

- 5: connect to random comm. resource

- 6: for all comm. resources connected to only one comp. resource do

- 7: connect to random comp. resource

- 8: Random pruning of superfluous connections

# V. PLATFORM GENERATION

Automatically generated platform models should resemble the architecture of real-world systems to provide a sensible basis for evaluation. Thus, in order to be applicable to various application domains an algorithm for generation of platform models should be parameterizable to produce a wide range of different architectures. We have implemented an exemplary algorithm that allows to influence the size (i.e. number of computational resources) and degree of connectivity (i.e. communication structure between computational resources) of generated platform models.

The algorithm produces platform graphs that are one bipartite connected component. Furthermore it ensures, that each communication resource is connect to at least 2 computational resources. Algorithm 1 shows the pseudo-code for the platform generation. The algorithm requires the two parameters numRes and CRes%. numRes directly defines the number of computational resources in the system. It allows the user to scale the overall system size. The second parameter (CRes%) controls the degree of connectivity of the platform. It allows to set the average number of communication resources as percentage of the number of computational resources. E.g. if set to 5%, on average the generated platforms will have 0.05 times as many communication resources as computational resources. As a result low values of CRes% will tend to generate bus-like architectures, while higher values will tend to create architectures with gateways.

First, the algorithm determines the number of communication resources based on a binomial distribution (line 1). Then the algorithm ensures that all communication resources are contained in one connected component (lines 2-3), that all comp. resources are connected to at least one comm. resource (lines 4-5) and that all comm. resources are connected to at least two comp. resources (lines 6-7). In a last step (line 8) connections are pruned, such that no two computational resources are connected to the same two communication resources, if this does not violate any of the required platform criteria.

#### VI. APPLICATION GENERATION

As platform models, also application models are highly diverse for different domains (e.g. highly parallel applications vs. sequential task graphs). TGFF [11] already provides sophisticated algorithms for parameter-driven task graph generation allowing to reflect this diversity. It has been used extensively in various projects (e.g. [12], [13], [14]). The exemplary algorithm of SMFF is based on TGFF but extends the functionality by support for cyclic task graphs. The remaining parameters are identical to the old algorithm of TGFF (for a complete description of TGFF's functionality refer to [20]).

#### Algorithm 2 Application Generation

| INPUT: | numTasks,     | diffNumTasks,   | taskMaxDegrIn,   | taskMaxDegrOut,   |

|--------|---------------|-----------------|------------------|-------------------|

| су     | clicGraph     |                 |                  |                   |

| 1: get | task graph fi | rom TGFF(numTas | ks, diffNumTasks | s, taskMaxDegrIn, |

| ta     | skMaxDegrO    | ut)             |                  |                   |

| 2: if  | cyclicGraph   | n then          |                  |                   |

| 2.     | - 1º . 1      |                 |                  |                   |

- undirect edges

find cycles

- 4: find cycles 5: redirect edges

- 6: convert task graph to application model

Algorithm 2 shows the application model generation in pseudo-code. The first four parameters (numTasks, diffNumTasks,taskMaxDegrIn, taskMaxDegrOut) are passed directly to TGFF (line 1). TGFF can only create non-cyclic task graphs. If cycles are allowed in the created applications (parameter cyclicGraph, line 2), the direction of all edges of the task graph is deleted (line 3). A cycle search is performed on the undirected graph (line 4) and edges are re-directed (line 5). In a final step (line 6) the task graph is transformed to the framework's application model.

#### VII. APPLICATION MAPPING

The application mapping completes the structural definition of a system model and determines the degree of distribution of an application on the platform. Applications may be either clustered, i.e. all tasks are located on only a few resources, or widely spread, i.e. tasks are distributed across many resources. However some domains may have very specific requirements on application mapping. E.g. if the generated system model should resemble a client-server setup, a path of the application graph should start and end on the same resource while some intermediate task has to be mapped on a different resource.

The example mapping algorithm is tailored to generate mappings for "sensor-actuator-like" applications. More specifically, it only maps two tasks of an application on the same resource, if they are adjacent in the application model. At the same time it tries to distribute the tasks of the application across several resources. This mapping is performed by a probabilistic algorithm that enforces the first criterion and lets the user control the degree of distribution with a parameter. The algorithm only supports chains of tasks without forks and joins. Its pseudocode is shown in Algorithm 3.

As long as the application is not completely mapped (line 2) the algorithm alternatingly selects the first/last task of the task chain, that is not yet mapped (lines 3-6). For the selected task the set of resources, that this task can be mapped on, is calculated based on distances in the platform graph and the distances to already mapped tasks of the application graph (line 7). In the following step a probability with which the task is mapped to a resource is calculated for every resource in this set (line 8). This step is based on a weighted random number generator, which selects a value from a given set with a probability corresponding to the value's weight (nonnormalized probability mass). The probabilities for all other resources are initialized with 1 and are then modified by the three parameters that are passed to the mapping algorithm. kPredecessor and kSuccessor are factors applied to the weight of a resource, if the predecessor or successor of the task to be mapped, is mapped on a resource (line 8). The third parameter kResDist is applied only to the end

#### Algorithm 3 Application Mapping

|     | f: kPredecessor, kSuccessor, kResDist<br>emp=0         |

|-----|--------------------------------------------------------|

| -   | while not all tasks mapped do                          |

| 3:  | if (temp++)%2==0 then                                  |

| 4:  | get first unmapped task of task chain                  |

| 5:  | else                                                   |

| 6:  | get last unmapped task of task chain                   |

| 7:  | calculate set of possible resources                    |

| 8:  | calculate probability of all possible resources        |

| 9:  | if temp==2 then                                        |

| 10: | apply kResDist to probabilities                        |

| 11: | map task on resource based on probability distribution |

of the task chain. Each resource's weight is multiplied by kResDist<sup>distance</sup>, where distance is the distance to the resource that the first task was mapped on (line 10). Thus, kResDist allows to control the degree of distribution of an application. In a final step a resource is chosen from the set of possible resources based on probability mass and the task is mapped to that resource.

# VIII. DEFINITION OF REAL-TIME PROPERTIES AND CONSTRAINTS

The previous three sections have elaborated on the algorithms for the structural definition of a system model. Now, we focus on the remaining steps of timing property and scheduling parameter assignment and generation of constraints. Depending on the developer's needs these three steps may be closely related; e.g. if testcases are required where some constraints are violated, the assignment of timing properties and scheduling parameters have to be performed beforehand.

#### A. Assignment of Scheduling Parameters

Along with the framework we provide an exemplary algorithm for assignment of scheduling parameters for SPP scheduled resources. Execution priorities for tasks and task links are assigned randomly. Execution priorities that were set beforehand are left unchanged.

#### B. Assignment of Timing Properties

In this step of testcase generation the timing properties of all tasks and task links are defined. In the example algorithm of SMFF this comprises assignment of an activation period, an activation jitter, BCET and WCET. SMFF uses the UUniFast algorithm presented in [16] for this step. UUniFast assigns task execution times, such that the resource utilization assumes a specified value, while the distribution of the task execution times is uniform.

In the SMFF implementation of UUniFast activation periods are assigned uniformly in a specified interval [minActPeriod, maxActPeriod]. The user furthermore specifies an interval for resource utilization [minResU, maxResU]. From this interval a random value is chosen for each resource and the task execution times are assigned according to UUniFast to achieve that resource utilization. BCETs are assigned as user-specifiable percentage of WCETs [bcetPercentage].

#### C. Assignment of Timing Constraints

The assignment of timing constraints for a testcase system model is of particular importance when evaluating algorithms for optimization or design space exploration, as it may significantly influence the number of feasible system configurations

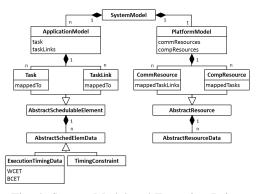

Fig. 3: Organization of System Generation Stages

(i.e. configurations that do not violate any constraint).

The implemented algorithm is again targeted at sensoractuator-like applications. It defines paths from the first task to the last task of a task chain. The value of the constraint is defined as multiple of the sum of all WCETs along the path. This factor - the constraint *laxity* - is randomly selected from a user-defined interval [minLaxity, maxLaxity]. Smaller laxity values result in more tightly constrained systems.

#### IX. IMPLEMENTATION AND MODULARITY

Until now we have focused on the testcase generation algorithms of the SMFF framework. However, as previously indicated, requirements on generated system models may be diverse, depending on application domain, scheduling algorithm and algorithm under evaluation. Thus the presented implementations of the generation steps may not be suitable for every user and the system model might not be sufficient. To account for the diverse requirements the testcase generation framework is implemented in a modular way, allowing extension of the data structures as well as replacement of all generation steps. The framework was implemented in Java for ease of development and platform independence. The next paragraphs give a short overview of the software architecture of SMFF, highlighting the aspects of modularity and extensibility.

# A. Model Generation Infrastructure

In order to enable a flexible combination of the system model generation steps described in this paper, SMFFs generation logic is based on an aggregation of factories, each responsible for one step of the generation process. For an overview refer to fig. 3. All factories are grouped in a central system generation factory orchestrating the order of the single generation steps. The SMFF model generation core library as depicted in fig. 3 does not provide any generation logic, but merely defines the relationship between the single factories and their APIs to ensure seamless integration of different implementations of the model generation stages. An actual implementation, as the one discussed in this paper needs to provide an implementation for each of the factories.

The algorithms described in this paper are shipped with

Fig. 4: System Model and Extension Points

SMFF as standard implementations, e.g. StdPlatformFactory. As an example, fig. 3 shows two additional possible implementations of a platform factory (AutomotivePlatformFactory, FixedPlatformFactory), which could be integrated into the flow. This shows that a user of the tool may replace e.g. the standard platform generation logic with a platform factory specific to his own requirements, while using the standard implementations of the other factories for the remaining steps.

Similarly, e.g. the default order imposed on the stages of system model generation can be altered by replacing the standard implementation of the system factory.

#### B. Model Representation

Next, we present the system model data structure as shown in fig. 4. It consists of a platform model and multiple application models. Platform models are comprised of computational and communication resources, represented by the CommResource and CompResource class respectively. Similarly, application models consist of tasks and task links, each represented by a distinct class. Additionally, application and platform models manage adjacency information about their parts defining the bipartite graphs described in section IV. A mapping is specified as a relation between task or task links and communication and computational resources. In the diagram this is indicated by the relevant local variables.

In order to reflect the flexibility of the model generation framework also in the system model data structure, all model elements allow the attachment of additional classes for extension of data and functionality without modification of the basic data structure. Fig. 4 shows that application as well as platform model components may be associated with a set of data elements. Although not shown in the figure, data extension points also exist for the system, application and platform models, thus enabling a very flexible extension of the model depending on the specific use-case of SMFF.

#### C. Framework Extensions

This flexible data structure allows usage of the generation framework for multiple purposes. For example, we implemented an interface to the performance verification tool SymTA/S [21] to allow verification of timing constraints. This also allows to e.g. only generate systems that are schedulable. All relevant data and functionality needed to transform the system model to a SymTA/S compliant representation as well as retrieving data from the SymTA/S tool is encapsulated in data extensions of model elements. Another existing extension

#### Algorithm 4 Sample System Model Generation

- **INPUT:** systemFactoryData

- 1: // create system factory 2.

- StdSystemFactory systemFactory = new StdSystemFactory(systemFactoryData); 3. // create new system model

- 4: SystemModel = systemFactory.generateSystem();

- 5: // create XML file

- 6: new ModelSaver("SystemModel.xml").saveModel(systemModel); 7: // create PDF file

- 8: PdfPrinter.convertToPdf(systemModel, "systemGraph.pdf");

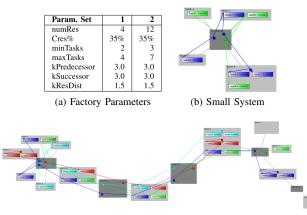

(c) Large System

Fig. 5: Example Systems generated with SMFF

is a Visualization Plugin to the SMFF framework. It enables the display of a graph representation of the system model as well as the export to a pdf file. This allows the user to quickly grasp the platform and application graphs and the application mappings of the generated system models. The XML Load/Store Plugin completes the SMFF model generation suite, allowing easy integration with other tools.

## X. TESTCASE GENERATION EXAMPLE

In this section, we give a brief example on how to use SMFF in practice. We assume that all necessary factories for the system generation stages are present. We used the algorithms specified earlier on in this paper for generation of the example systems shown below.

Algorithm 4 shows the necessary code to generate a system from a set of parameters as needed for the different model generation stages, which we assume to be given. In order to generate a system model, one merely needs to instantiate a system factory, in this case the StdSystemFactory supplied with SMFF (line 2). A system model is generated each time the generateSystem() function of the factory is called (line 4). The following lines show the code necessary to save the model to an XML file (line 6) and create a pdf file (line 8) containing a graphical representation of the system.

Fig. 5 shows two example systems that have been generated by SMFF and exported using the visualization plugin. The relevant parameters to the system model generation algorithms as described in the previous sections are summarized in figure 5a. The parameters in column 1 resulted in the system model shown in fig. 5b, the model shown in fig. 5c corresponds to the parameter set in the second column. Note that multiple application models were generated for both systems. Each application model is depicted in a separate color.

#### **XI.** CONCLUSION

In this paper we have presented System Models for Free (SMFF) - a framework for parameter-driven generation of models of distributed real-time systems. SMFF can generate completely specified system models, including specification of platform architecture, of application models, mapping of applications and definition of timing and scheduling parameters and timing constraints.

As illustrated with examples, the user can easily and quickly generate pseudorandom system models for use in his field of application, thanks to supplied standard implementations of parameter-driven factories. More advanced users can take advantage of the flexible infrastructure of SMFF, by replacing implementations of system generation steps or extending the system model to tailor SMFF to fit their specific needs.

If you would like to use SMFF in your project, feel free to contact any of the authors or visit http://smff.sourceforge.net.

#### REFERENCES

- [1] M. Neukirchner, "System models for free (smff)," Internet. [Online].

- M. Neukirchner, System models for free (smir), Internet. [Online].

Available: http://smif.sourceforge.net

M. Neukirchner, S. Stein, and R. Ernst, "A lazy algorithm for distributed priority assignment in real-time systems," in *Proc. of 2nd IEEE Workshop on Self-Organizing Real-Time Systems (SORT)*, 2011.

S. Perathoner, E. Wandeler, L. Thiele, A. Hamann, S. Schliecker, D. Hardbard, D. B. Bard, and M. C. Lucher, Windows and Schliecker, Schliecker, Stranger, Stranger, S. Schliecker, State and Schliecker, Schliecker, Stranger, Schliecker, S [2]

- [3] R. Henia, R. Racu, R. Ernst, and M. G. Harbour, "Influence of different abstractions on the performance analysis of distributed hard real-time,

- [4] J. Real and A. Crespo, "Mode Change Protocols for Real-Time Systems: A Survey and a New Proposal," *Real-Time Systems*, vol. 26, pp. 161– 197, 2004.

[5] J. G. García and M. G. Harbour, "Optimized priority assignment for for detailed and a superscription of the optimized priority assignment for for the optimized back and the optimized priority assignment for for the optimized back and the optimized priority assignment for for the optimized back and the optimized priority assignment for for the optimized back and the optimized priority assignment for for the optimized back and the optimized back and the optimized priority assignment for for the optimized back and the optimized back a

- tasks and messages in distributed hard real-time systems," in Proc. of the

- IEEE Workshop on Parallel and Distributed Real-Time Systems, 1995. T. Cucinotta and L. Palopoli, "QoS Control for Pipelines of Tasks using Multiple Resources," IEEE Trans. on Computers, vol. 59, pp. 416–430, [6] 2010

- A. R. Weiss, "The standardization of embedded benchmarking: pitfalls and opportunities," in *Int'l. Conf. on Computer Design (ICCD)*, 1999. [7]

- T. D. ter Braak, P. K. F. Hölzenspies, J. Kuper, J. L. Hurink, and G. J. M. [8]

- [6] F. D. Boltaka, F. R. F. HOLLSPIES, S. Haper, J. J. Hamil, and G. S. M. Smit, "Run-time spatial resource management for real-time applications in heterogeneous mpsocs," in *Proc. of DATE'10*, 2010.

[9] B. Andersson, S. Baruah, and J. Jonsson, "Static-priority scheduling on multiprocessors," in *Proc. 22nd IEEE Real-Time Systems Symp. (RTSS)*, 2020. 2001

- [10] J. M. Calandrino, H. Leontyev, A. Block, U. C. Devi, and J. H. Anderson, "LITMUS<sup>RT</sup>: A Testbed for Empirically Comparing Real-

- Time Multiprocessor Schedulers," in *RTSS*, 2006. [11] R. P. Dick, D. L. Rhodes, and W. Wolf, "TGFF: task graphs for free," in *Proc. of the 6th Int'l. workshop on Hardware/software codesign* CODES/ČASHE), 1998.

- [12] V. Kianzad, S. Bhattacharyya, and G. Qu, "Casper: an integrated energy driven approach for task graph scheduling on distributed embedded

- systems," Application-Specific Systems, Architecture Processors, 2005. ASAP 2005. 16th IEEE Int'l. Conf. on, pp. 191–197, 2005.

[13] M. Schmitz, B. Al-Hashimi, and P. Eles, "Energy-efficient mapping and scheduling for dvs enabled distributed embedded systems," in *Proc. of the conf. on Design, automation and test in Europe (DATE)*, 2002.

- [14] L. Shang and N. K. Jha, "Hardware-software co-synthesis of low pow real-time distributed embedded systems with dynamically reconfigurable fpgas," in VLSI Design, 2002

- [15] E. Bini, G. Buttazzo, and G. Buttazzo, "A hyperbolic bound for the rate monotonic algorithm," in *Proceedings of the 13th Euromicro Conference*

- on Real-Time Systems, 2001.

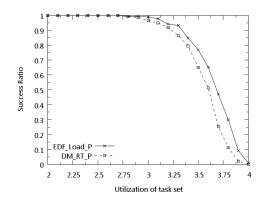

[16] E. Bini and G. Buttazzo, "Measuring the performance of schedulability tests," *Real-Time Syst.*, vol. 30, pp. 129–154, 2005.

- [17] E. Bini, T. H. C. Nguyen, P. Richard, and S. Baruah, "A response-time bound in fixed-priority scheduling with arbitrary deadlines," Computers, IEEE Transactions on, vol. 58, pp. 279–286, 2009.

- [18] V. Pollex, S. Kollmann, K. Albers, and F. Slomka, "Improved worst-case

- response-time calculations by upper-bound conditions," in *DATE*, 2009. [19] F. Zhang and A. Burns, "Schedulability analysis for real-time systems with edf scheduling," *Computers, IEEE Transactions on*, vol. 58, pp. 10270202020 [20] K. Vallerio, *Task Graphs for Free (TGFF v3.0)*, April 2008.

[21] R. Henia, A. Hamann, M. Jersak, R. Racu, K. Richter, and R. Ernst,

- 'System level performance analysis the symta/s approach," Computers and Digital Techniques, IEE Proc. -, vol. 152, pp. 148-166, 2005.

# On the Gap between Schedulability Tests and Automotive Task Model

Saoussen Anssi<sup>1</sup>, Stefan Kuntz<sup>1</sup>, Sébastien Gérard<sup>2</sup>, François Terrier<sup>2</sup> <sup>1</sup>Continental Automotive France SAS, PowerTrain E IPP 1 Avenue Paul Ourliac - BP 83649, 31036 France {saoussen.ansi, stefan.kuntz}@continental-corporation.com <sup>2</sup>CEA LIST, Laboratory of model driven engineering for embedded systems, Point Courrier 94, Gif-sur-Yvette, F-91191 France { sebastien.gerard, francois.terrier}@cea.fr

Abstract- In this paper, we study the adequacy of available schedulability tests for monoprocessor fixed-priority systems to enable performing scheduling analysis for automotive applications. We show that, in spite of the work carried out during the last decade to enhance these tests in order to support more realistic task model, a gap still exists between the task model considered in these tests and automotive task model. However, we claim that an extension of these tests is possible to support some of the uncovered automotive features. The aim of this study is to raise discussion and make researchers involved in the development of such schedulability tests be aware of the gap still existing between current schedulability tests and automotive task model. The study is illustrated by showing the concrete challenges faced when applying scheduling analysis to a real automotive case study.

#### I. INTRODUCTION

Today, embedded automotive systems often involve hard real-time constraints intended to ensure full system correctness [1]. Power train and chassis applications, for example, include complex (multi-variable) control laws, with different sampling periods, for use in conveying real-time information to distributed devices. One hard real-time constraint controlled in power train applications is ignition timing, which varies with engine position. The latter is defined by a sporadic event characterizing the flywheel zero position. End-to-end response times must also be bounded, since a too long control loop response time may not only degrade performance, but also cause vehicle instability. These constraints have to be met in every possible situation.

Automotive software development costs are sharply impacted by wrong design choices made in the early stages of development but often detected after implementation. Most timing-related failures are detected very late in the development process, during implementation or in the system integration phase. Timing verification is usually addressed by means of measuring and testing rather than through formal and systematic analysis. For this reason, innovative and complex functionalities are not implemented in a cost-efficient way<sup>1</sup>. The benefits of defining an approach that permits early timing verification for automotive systems are thus obvious. Such an approach would enable early prediction of system timing behavior and allow potential weak points in design to be corrected as early as possible

In this context, we aim at developing an approach that enables automotive system designers predicting early the timing behavior of a system before the costly implementation phase of a project begins.

Quantitative analysis techniques (such as scheduling or performance analysis) are good candidates for analyzing non-functional properties for automotive applications. Using these techniques, designers could detect infeasible real-time architectures, and therefore prevent costly design mistakes, while providing an analytical basis for assessing the design tradeoffs associated with resource optimization. For these reasons, in our approach, we suggest to use the scheduling analysis as an early verification technique for automotive systems.

Task scheduling and schedulability analysis have traditionally been the most studied topics within the field of real-time systems [2]. The problem of scheduling fixed-priority task set with hard deadlines on a uniprocessor was first studied by Liu and Layland. They gave a worst case performance analysis of the rate monotonic scheduling algorithm [3]. Liu and Layland work has come through the work of a large group of researchers who extended it in a number of ways. For instance, many necessary and sufficient feasibility tests have been developed to predict the schedulability of a

<sup>&</sup>lt;sup>1</sup> These statements are based on the study of current automotive software development practices and particularly in the case of Continental

task set. These tests are based on the calculation of the worst-case response time of a task, which is the longest time between the arrival of a task and its subsequent completion. The feasibility of the task can be checked by comparing its worst-case response time to its deadline.

Adapting these schedulability tests to enable scheduling analysis for automotive applications has been tackled by some recent academic studies [4] but it is still in its very beginning. Results from these works will be discussed later in this paper. Some commercially available scheduling analysis tools, such as SymTA/S [5] are said to be based on techniques extending such feasibility tests to take into account automotive task model specificities. However, information about the algorithms used in these techniques is not publicly available.

In this paper, we aim at determining the extent to which some of these tests can be used to perform scheduling analysis for automotive applications. This means answering the following questions: to what extent the task model considered in these tests do map a realistic automotive task model. To answer this question, we firstly propose a characterization of an automotive task model; we list the most important features that should be considered when developing a schedulability test for such task model. Then, we show to what extent the available feasibility tests satisfy these features. Although, we show that some features are already covered by some schedulability tests, we conclude that a gap still exists between automotive task model and the assumptions considered in such feasibility tests. However, we claim that an extension of some of these tests is possible to support some of the uncovered automotive features.

The paper is organized as follows. In section II, we give a characterization of automotive task model. Then, in section III we present a brief state-of-the art of the available schedulability tests and show to what extent they cover the automotive task model features. Section IV is dedicated to highlight the challenges met to apply schedulability analysis to automotive systems. This is done through performing scheduling analysis to an automotive use case using an open source tool that implements some of the studied schedulability tests.

# II. AUTOMOTIVE TASK MODEL

In this section, we present a characterization of automotive task model. We consider task model of monoprocessor applications based on OSEK/VDX, i.e. with a fixed priority scheduling. The features listed in this section have been collected based on the author's experience in the automotive domain and particularly in Powertrain context at Continental.

Automotive task model is characterized by the following features:

- Arbitrary deadlines: Automotive tasks may have deadlines less, equal or greater than their periods. Deadlines greater than periods are used for functions that are distributed over several processors. In this case, the deadlines of these functions are a sort of end-to-end deadlines that can be greater than function periods.

- Offsets/variable offsets: In an automotive application, a task start may be delayed by a value called offset or phasing. The particularity of some automotive tasks is that their phasing depends on the variable engine speed.

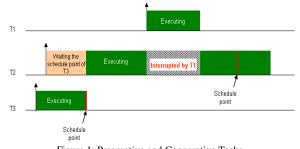

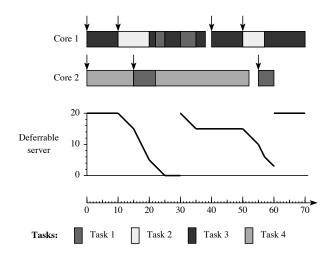

- Preemptive and cooperative tasks: In automotive applications, there are two kinds of tasks: Preemptive tasks and cooperative tasks. Preemptive tasks can be interrupted by higher priority tasks at any time and can interrupt any lower priority task at any time of its execution. Cooperative tasks can be interrupted by higher priority cooperative tasks only in predefined points called schedule points. Figure 1, shows an example of a system with preemptive and cooperative tasks. Task T1 is a preemptive task having the highest priority, task T2 and T3 are both cooperative tasks, T2 has got higher priority than T3. As the figure shows, T2 waits until the schedule point of T3 to start executing while T1, being preemptive, interrupts T2 before its schedule point.

Figure 1: Preemptive and Cooperative Tasks Cooperation is needed in automotive task model to ensure data consistency while avoiding a long blocking time of higher priority tasks that may result from fully non-preemptive tasks.

• Same priority level: In automotive task model, different tasks may have the same criticality and hence the same priority level is assigned to them. To schedule these tasks the FIFO (First In First Out) protocol is used. This means that if two tasks having the same priority are waiting to start executing, the task that was activated first will start its execution first.

- **Dependant tasks:** In automotive task model, task dependency may result from the use of shared resources. It may also result from precedence relationship between tasks called "task chaining" where the activation of a task is triggered by the termination of its predecessor. In Powertrain applications, task chaining is needed to enable e.g. the activation of timing tasks by the OS clock where this clock is modeled as a periodic task that triggers other tasks at the end of each instance of it.

- Heterogeneous recurrences: In automotive task model, tasks can be time-triggered or event triggered. Event triggered tasks are activated by the arrival of events that can be sporadic or singular (arrives only once). Time-triggered tasks are periodic tasks that are activated at predetermined points in time. In automotive, there are two kinds of periodic tasks, timing tasks and enginesynchronous tasks. Timing tasks have timing recurrences (e.g. 1ms, 10ms, etc). Enginesynchronous task recurrences are expressed in engine angle degree rather than time (e.g. 2°crk). In fact these recurrences depend on the Camshaft and Crankshaft positions that vary with the engine speed (The camshaft is the element of the engine that allows the opening and the closure of intake and exhaust valves. The crankshaft is the part of the engine that translates reciprocating linear piston motion into rotation). Hence, expressing the period of such tasks in time depends also on the engine speed. For instance, for a 6 cylinder system, a task that should be activated each 120°crk has got a recurrence of 3.3ms at 6000rpm and 13.33ms at 1500rpm. This variable aspect of recurrence should be taken into account when designing a schedulability test for such task model.

- Changing execution profile: The execution time of some automotive tasks depend of the engine speed. For instance, some tasks are deactivated beyond a certain speed (i.e. their computation time becomes zero). Hence, to analyze the real time behavior of such systems, the schedulability test used should take into account task variable execution times.

- Self-suspending tasks: During its execution, a task may suspend itself to wait for one or more event.

- System overheads: In automotive task model, overheads may results from: the computation time required to activate a task, the computation time

required to schedule the tasks, the computation time to terminate a task and reschedule and finally the computation time to lock and unlock a resource.

# III. ADEQUACY BETWEEN SCHEDULABILITY TESTS AND AUTOMOTIVE TASK MODEL

This section studies to what extent, the abovementioned task model features are supported by the available schedulability tests. First, we present a brief historical review of the development of these tests (we focus on tests developed for fixed priority systems). In the second part we discuss to what extent the automotive task model features are supported by these tests.

# A. Schedulability Tests: Brief historical review

In this section, we present a historical review of the most known results achieved within schedulability test development for fixed-priority monoprocessor systems In 1973, Liu and Layland published a paper on the scheduling of periodic tasks that is generally regarded as the foundational and most influential work in fixed priority real time scheduling theory [3]. They considered the following assumptions: 1) all tasks are periodic, 2) all tasks are released at the beginning of period and have a deadline equal to their period, 3) all tasks are independent, i.e., have no resource or precedence relationships, 4) all tasks have fixed computation time or, at least, an upper bound on their computation time which is less than or equal to their periods, 5) no task may voluntary suspend itself, 6) all tasks are fully preemptible, 7) all overheads are assumed to be (0, 8)there is just one processor. Based on this model, Liu and Layland gave a sufficient utilization-based condition for the feasibility of a fixed priority task set scheduled with the rate monotonic algorithm [3]. They proved that a set of n periodic tasks, each having a computation time C<sub>i</sub> and a period T<sub>i</sub> is feasible with this algorithm if

$$\sum_{i=1}^{n} \frac{C_i}{T_i} \le n \left( 2^{\frac{1}{n}} - 1 \right)$$

Due to the limitations of Liu and Layland test (pessimistic condition, unrealistic task model with deadlines equal to periods, task priorities have to be assigned according to the rate monotonic policy) more complex feasibility tests were developed to address the above limitations. In 1987, Lehoczky et al. [6] gave the first exact schedulability test for the Liu and Layland task model. Concurrently, another group of researchers looked at the problem of determining the worst case response time of a task. Joseph and Pandya [7] and Audsley et al. [8] developed independently an algorithm to compute the worst-case response time  $R_i$  of a task  $\tau_i$  as the least-fixed-point of the following recursive equation:

$$R_i = C_i + \sum_{j=1}^{i-1} \left| \frac{R_i}{T_j} \right| C_j$$

In 1982, Leung [9] considered fixed priority scheduling of a set of tasks with deadlines less than their periods. Lehoczky [10] considered another relaxation of the Liu and Layland model to permit a task to have a deadline greater than its period. The Lehoczky approach uses the notion of "busy-period". A "level i busy period" is defined as the maximum time for which a processor executes tasks of priority greater than or equal to the priority of task i. Lehoczky shows how the worst-case response time of a task i can be found by examining a number of windows, each defined to be the length of the busy period starting at the window, and each window starting at an arrival of task i. In the early 1990, Tindell [11] extended the Lehoczky response time analysis providing an exact test for tasks with arbitrary deadlines.

A further relaxation of Liu and Layland task model is to permit tasks to have specified offsets (phasing). Tindell proposed in [12] a test for fixed priority tasks in which task offsets can be taken into account. This test has been later extended to by Palencia and Gonzalez [13].

Wang and Saksena [14] introduced a feasibility test where they take into account non-preemptible tasks in addition to preemptible ones.

#### B. Schedulability Tests Evaluation

As shown in the previous section, many feasibility tests have been developed to extend the Liu and Layland original test and be closer to a realistic task model. In this section, we show to what extent the automotive task features presented previously are supported by these tests. We give also some suggestion of possible extensions of some of these tests to support the uncovered features.

• Arbitrary deadlines: For automotive task model, the schedulability test should support tasks with deadlines less, equal or greater than periods. The Leung [9] test remains incomplete as it assumes that deadlines are either less or equal to periods. It is the same case for the Lehoczky [10] test as it considers only tasks with deadlines greater than periods. In addition, Lehoczky test restrict all tasks to have  $D_i = kT_i$  where k is constant across all tasks. However, the Tindell test [11] for tasks with arbitrary deadlines can be used as it allows deadlines to be less, equal or greater than periods. In addition, unlike the test proposed by Lehoczky, the analysis given by Tindell places no restrictions upon the relative task periods. Hence, the Tindell test described in [11] supports the arbitrary deadlines feature of automotive task model. However, to use this test, the remaining features should also be covered

- Offsets/variable offsets: The Tindell test [11] described above assumes that all tasks are released at beginning of period. Hence this test is incomplete and does not allow accurate analysis for automotive tasks with offsets. However, Tindell developed a second test [15] that allows tasks to have offsets. In this test the concept of transaction is introduced. A transaction is a collection of related tasks and it has got a period. A member task of a transaction no longer has a specific period associated with it; it has rather an every attribute ei whereby it is permitted to run at most every e<sub>i</sub> transaction invocation. Task offsets are defined with reference to the start of the transaction and are assumed to be static and less than the period of the transaction. This test can be used for automotive tasks with static offsets. However, as mentioned previously, the offsets of some automotive tasks vary from one activation to the next, making, hence, the Tindell test inefficient to analyze such tasks. For such tasks, the test developed by Gonzalez and Palencia [13] can be used. This test extends the Tindell test for static offsets to allow analysis for tasks with static and dynamic offsets. It also enhances the Tindell test by allowing offsets to be greater than task periods. To be able to use this test to analyze automotive task model, the test should also take into account the feature described above, such as the mixed preemptive and cooperative scheduling.

- Preemptive and cooperative tasks: Unfortunately, the Palencia and Gonzalez test described above [13] assumes that all tasks are fully preemptible. It is the same also for the Tindell tests. Non preemptible tasks are considered in the Wang and Saksena test [14]. They defined the concept of preemption threshold that, as for task priority, is assigned offline and remains constant at run-time. When a task is released, it is inserted to the ready queue at its priority, when the task starts executing, its priority is raised to its preemption threshold and it keeps this priority until it finishes execution. Based on this model, they gave an algorithm to calculate the worst-case response time of tasks using the busy-period technique. The task model considered in

this test is slightly different from our model in term of preemptibility. In fact, in this test, a nonpreemptible task cannot be interrupted by a higher priority task until it terminates its execution. In our model, interruption of cooperative tasks by other cooperative tasks is forbidden only during the execution of task sections (code section between two schedule points). We think that such behavior can be captured with the notion of preemption threshold in a quite generic way by bringing this preemption threshold at the task section level rather than task level. This same approach is used in Hladik et al. test [4] to calculate the blocking time of a task due to the locking of a shared resource by a lower priority task in a simplified OSEK task model (more details about the Hladik test will be given in next section). Hence in our case the blocking time of a cooperative task T1 is the execution time of the longest section of a lower priority task T2 if this section has got a preemption threshold equal or greater than the priority of T1. In conclusion, the mixed preemption-cooperation aspect of automotive task model can be covered by extending the Wang and Saksena test. In addition, this test takes into account tasks with arbitrary deadlines as it is based on the extension of previous work such as the Tindell test for arbitrary deadlines. However, this test does not support tasks with static or dynamic offsets.

Same priority level: All the tests described above have been developed assuming different priority levels for different tasks except the Hladik et al. test [4]. In this test, Hladik gives a schedulability test for a simplified OSEK/VDX task model. In this model, tasks can be preemptive or not with arbitrary deadlines and shared resources. Moreover different tasks are allowed to have the same priority level and the FIFO scheduling is used for these tasks. The test uses the busy-period technique to calculate the worst-case response time for tasks. To calculate this response time, the test calculates first the worst case start time of an instance of a task. In this start time, the delay due to the execution of the tasks having the same priority level and activated before the considered task instance is added. The Hladik test covers hence more features then the previously described tests. However, this test does not take into account tasks with offsets. In addition, the test does not deal explicitly with cooperative tasks. Nevertheless, as mentioned before, this test adapts the preemption threshold notion to calculate blocking time due to shared resource locking. We think that this same approach can be used to calculate the blocking time due to the non-preemptible sections of cooperative tasks.

- Dependant tasks: Except the Hladik test, all the above mentioned tests assume that tasks are independent. The Hladik test described in [4] deals only with task dependency resulting from shared resource use. In this test, the OSEK IPCP protocol is considered for shared resource. Based on the work of Sha et al. in [16], The test considers that the worst-case blocking time of a task T is reduced to at most the duration of at most one critical section of a lower priority task that is using a resource whose ceiling priority is higher than or equal to the priority of task T. Hladik used the preemption threshold notion to calculate this blocking time showing that a task T can be blocked by at most one critical section of a lower priority task with a preemption threshold higher than or equal to the priority of T. In [17], Hladik et al. extend this test to take into account task chaining. However the test proposed is not an exact one since it presents only an upper bound of the worst-case response time.

- Heterogeneous recurrences: As mentioned previously, automotive task model contains both sporadic and periodic tasks. Periodic tasks have either timing recurrence or angular recurrence. Most of the schedulability tests presented above assume that tasks are purely periodic or sporadic with a known minimum inter-arrival time. Hence automotive periodic and sporadic tasks are taken into account. However, the problem remains unsolved concerning engine-synchronous tasks with angular recurrences. During engine running, the period of these tasks vary significantly making it impossible to consider a mean inter-arrival time for them. Moreover, these tasks present usually hard deadlines and have quite high priorities. In scheduling theory, tasks with such features are called aperiodic tasks. Among the work performed in system scheduling, most works focused on the problem of how to design feasible systems with such tasks [18], but none of the schedulability tests calculating the worst-case response times has considered this kind of tasks. As for a fixed engine speed the timing recurrence of engine-synchronous tasks is constant (hence they become purely periodic), one can think to use the above-mentioned schedulability tests to perform schedulability analysis at a fixed engine speed. However, the worst-case response times found for a particular speed are not valid for other engine speeds. Extending the available schedulability tests to cover all the engine

speeds seems to be intractable and inefficient. The main reason is that the computation of the response time is not an exact computation when the model becomes too complex.

- Changing execution profile: As mentioned previously, during engine running, the execution time of some tasks varies significantly as some treatments are performed or not depending on the current engine speed. Tasks with varying execution times have never been considered by the schedulability tests. All of them assume that tasks have a known maximum computation time. Extending these tests to take into account this variability in execution times seems also to be intractable.

- Self suspending tasks: self suspending tasks are not taken into account by schedulability tests. All of them assume that no task may voluntary suspend itself. However extending some of these tests to take into account this feature seems to be feasible. For example, one can use the transaction notion used in Tindell and Gonzalez tests [12, 13]. This way a self-suspending task can be modeled as a transaction composed of two tasks, the first task corresponds to the code before the suspension and the second task to the code after the suspension. As the activation of the second task depend on the computation time of the first one, the second task will have a variable offset. The work of Gonzalez on variable offsets can thus be used.

- System overheads: System overheads are assumed to be null in all above-mentioned tests. In [19], Bimard and Goerge give an algorithm to calculate the worst case response time of tasks where interference of kernel overheads are included into worst-case response time computation equation. In this test, overheads resulting from resource sharing are not considered as it assumes that tasks are independents. In addition this test does not take into account tasks with offsets as well as self suspending tasks.

#### C. Conclusion

As shown in the previous section, some features of the automotive task model are already handled by some of the available schedulability tests such as arbitrary deadlines and offsets. For other features such as engine-synchronous tasks and varying execution times which are quite important, they are unfortunately not taken into account. Extending the presented schedulability tests to end up with a final test covering all the necessary features seems to be quite challenging. On one hand, each of these tests focus only on some features and neglects the other (For instance tests dealing with offsets do not consider cooperative tasks while

tests dealing with non-preemptive tasks do not consider task offsets, etc). Hence one should find a way to combine the different techniques suggested in these tests. This means that ending up with an exact test is not guaranteed. Besides, engine-synchronous recurrences and variable execution times have never been tackled in these tests. This makes us think that extending these tests to cover these features is intractable. Although these evaluation results show that some automotive task model features can be covered by the extension/combination of some of these tests, they show also that a gap still exists concerning other features which are considered to be quite important in automotive applications.

#### IV. ILLUSTRATION

In this section, we show the concrete challenges faced when applying scheduling analysis to automotive applications. The work consists in performing scheduling analysis to an automotive use case using an open source tool, MAST [20], that is based on some of the above mentioned feasibility tests. The response times obtained are compared with values obtained from measurements done on the application using a test bench.

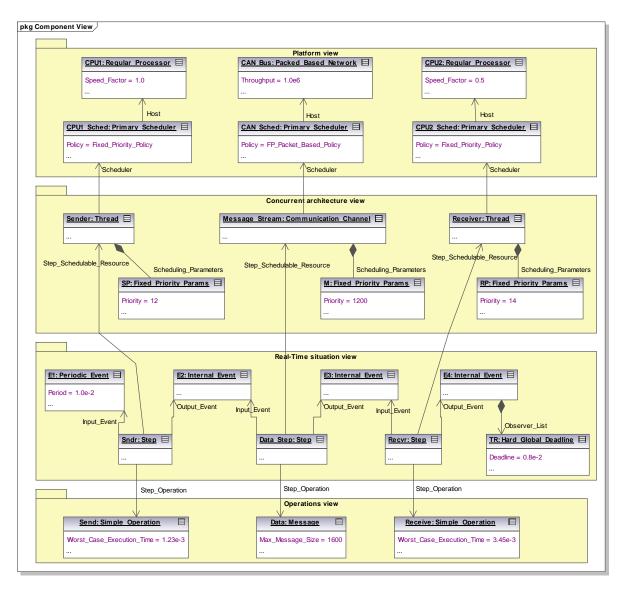

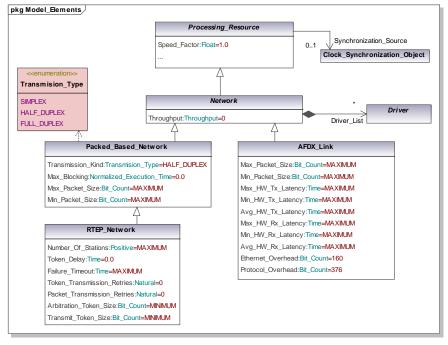

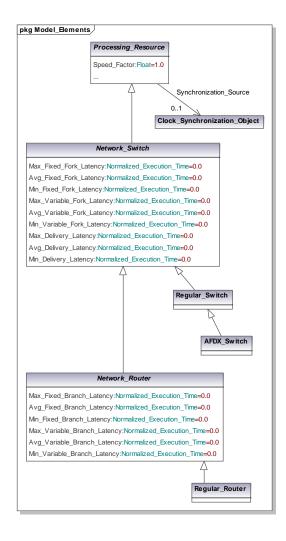

A. MAST overview

MAST is an open source tool that offers, for fixed priority systems, a suite of schedulability tests such as the RMA test developed by Liu and Layland [3] as well as the Gonzalez et al. test mentioned previously [13]. The tool also implements tests dedicated for distributed systems. The MAST model is based on the notion of transaction which represents a succession of interrelated activities. Each activity represents the execution of an operation which represent, itself a small segment of code execution. A transaction is characterized by an external event and a succession of activities. The output event of each activity in the transaction is the input event of the subsequent activity. For the first activity, the input event is the external event of the transaction. Tasks are represented by scheduling servers in MAST. A MAST scheduling server represents a schedulable entity in a processing resource. The allocation of operation to scheduling servers is ensured through the description of the corresponding activity.

## B. Use case presentation

The system to be analyzed is a simplified configuration of a Powertrain software platform. The Table below summarizes the tasks with their properties:

| Timing tasks |          |                  |                     |             |                                           |  |  |

|--------------|----------|------------------|---------------------|-------------|-------------------------------------------|--|--|

| Task         | Priority | Period<br>(ms)   | Deadline<br>(ms)    | Туре        | Sections<br>WCETs<br>(ms) **              |  |  |

| T1_T         | 9        | 1                | 0.2                 | Preemptive  | 0.14                                      |  |  |

| T2_T         | 7        | 5                | 0.5                 | Cooperative | {0.01}                                    |  |  |

| T3_T         | 4        | 10               | 10                  | Cooperative | {0.12, 0.09,<br>0.11, 0.05}               |  |  |

| T4_T         | 3        | 40               | 40                  | Cooperative | {0.38}                                    |  |  |

| T5_T         | 2        | 100              | 100                 | Cooperative | {0.27, 0.22,<br>0.29, 0.2,<br>0.25, 0.12} |  |  |

| T6_T         | 3        | 10               | 20                  | Cooperative | {0.29, 0.14,<br>0.2, 0.31}                |  |  |

|              |          | Engine-syn       | chronous task       | s           |                                           |  |  |

| Task         | Priority | Period<br>(°CRK) | Deadline<br>(° CRK) | Туре        | Sections<br>(ms) **                       |  |  |

| T1_ENG       | 5        | 120              | = period            | Cooperative | {0.7}                                     |  |  |

| T2 ENG       | 5        | 360              | = period            | Cooperative | {0.02}                                    |  |  |

| Table 2. I | ow | ertr | ain | task | c mod | lel |  |

|------------|----|------|-----|------|-------|-----|--|

|            | -  |      |     |      |       |     |  |

\*\* The WCETs used in this example were measured using internal method tools that for confidentiality reasons cannot be presented here

The "section WCET" column shows either the worst case execution time of the non-preemptible sections for a cooperative task or simply the worst case execution time of a preemptive task.

The periods of T1\_ENG and T2\_ENG depend on the Crankshaft position (measured in °crk) that, itself, depends on the engine speed. Some treatments performed by T1\_ENG are no more activated beyond 6500rpm, meaning that the computation time of this task changes beyond this speed. The enginesynchronous tasks should be executed in this order: T1\_ENG then T2\_ENG, we ensure this by introducing an offset of 45°crk on the activation of T2\_ENG. Hence, like periods, this offset varies also with the engine speed.

The Tasks T3\_T, T4\_T, T5\_T and T6\_T are activated by the termination of T2\_T. In addition, T3\_T and T6\_T which have the same recurrence are activated alternatively. This is ensured by introducing an offset of 5ms on the activation of T6\_T.

# C. Analysis challenges

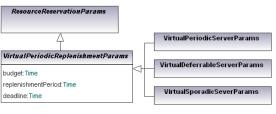

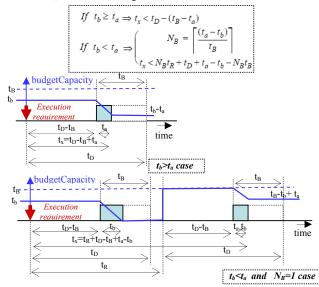

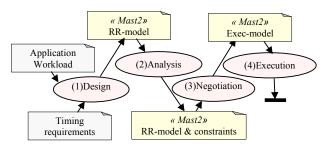

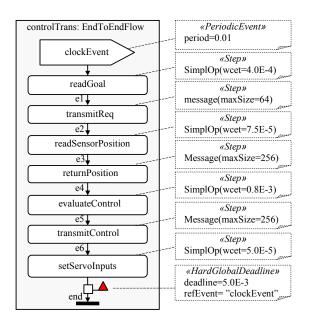

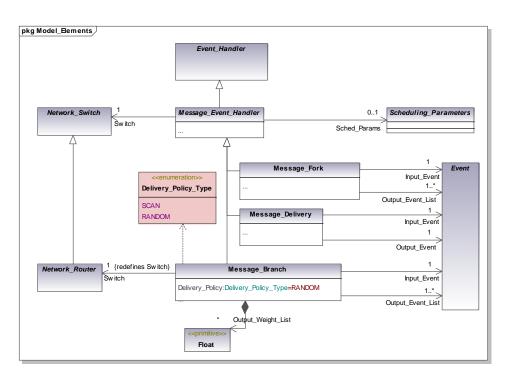

To analyze this system, we choose the Gonzalez et al. test [13] that is implemented in this tool as an "offset\_based" test. Although this test does not cover all the features of our model, it is the closest one among the tests available in this tool.