## Benefits of size reduction

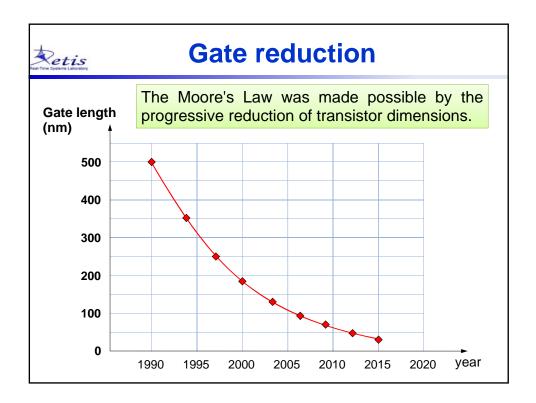

There are 2 main benefits of reducing transistor size:

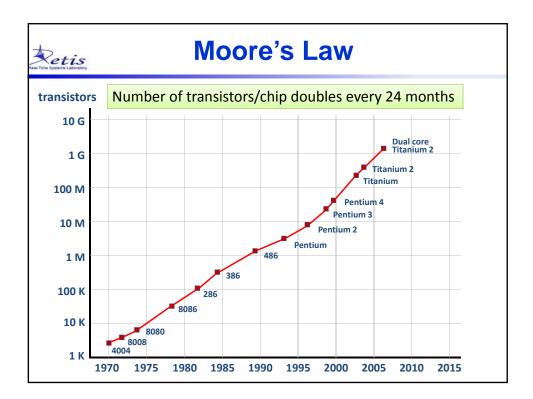

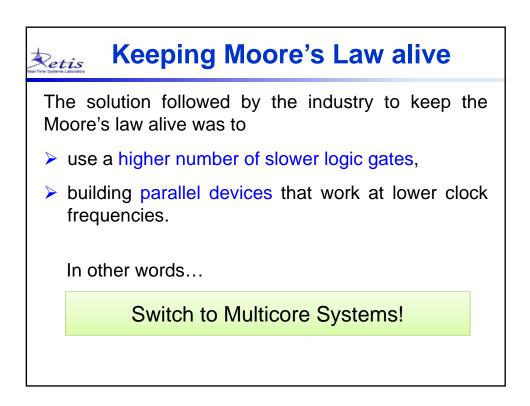

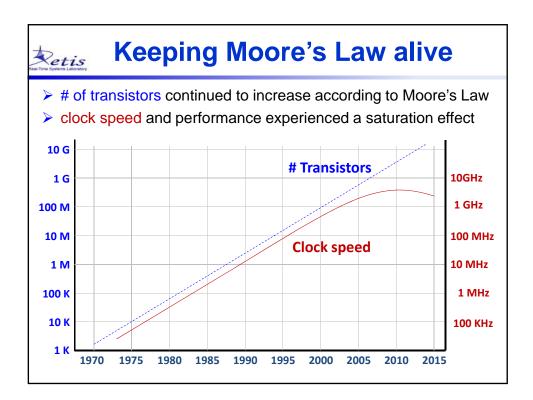

- 1. a higher number of gates that can fit on a chip;

- 2. devices can operate at higher frequency.

Retis

In fact, if the distance between gates is reduced, signals have to cover a shorter path, and the time for a state transition decreases, allowing a higher clock speed.

## However...

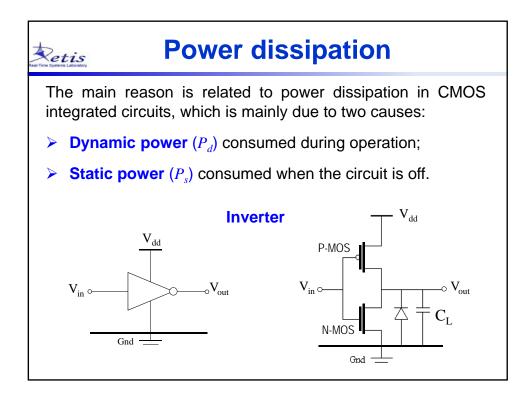

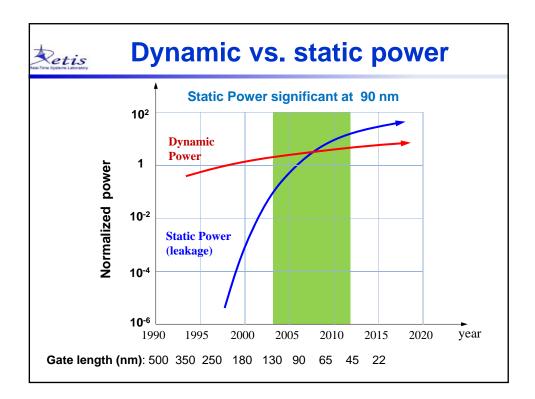

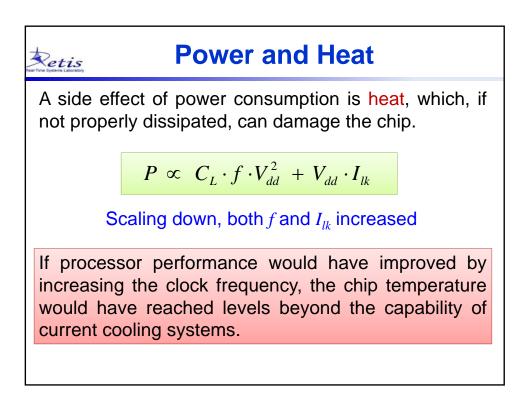

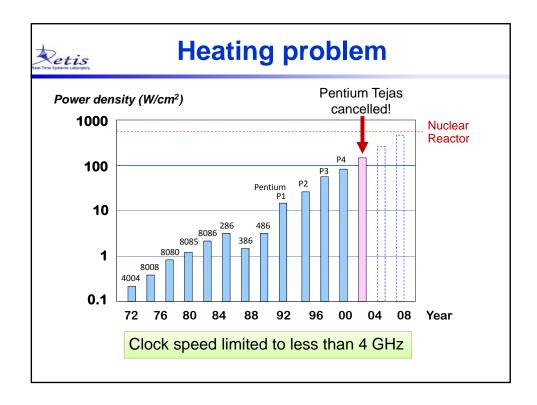

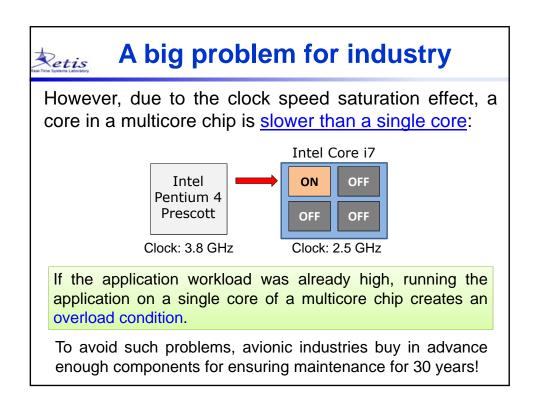

At the launch of Pentium 4, Intel expected single core chips to scale up to 10 GHz using gates below 90 nm. However, the fastest Pentium 4 never exceeded 4 GHz.

Why did that happen?

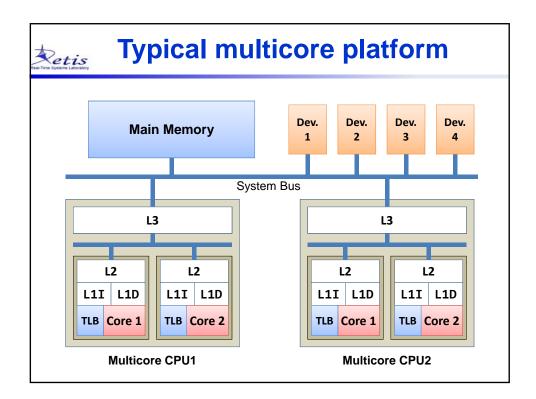

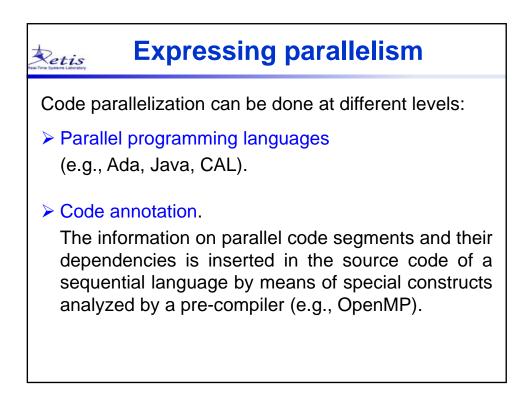

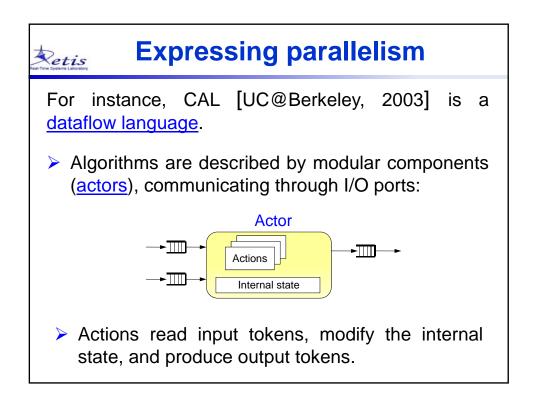

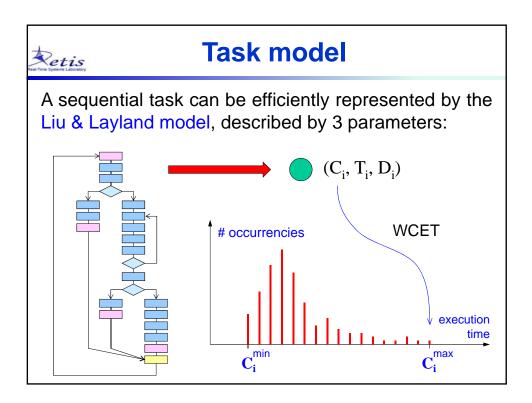

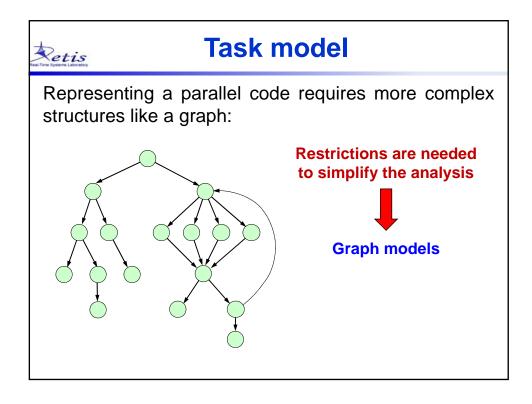

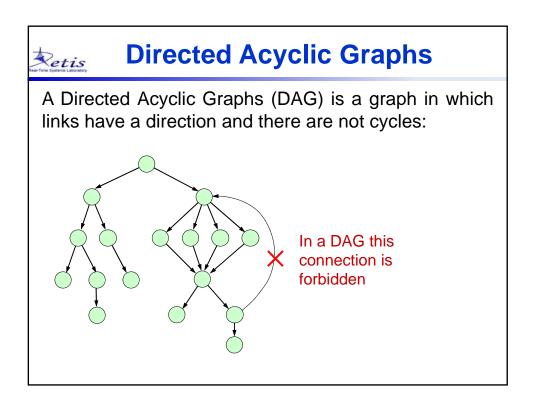

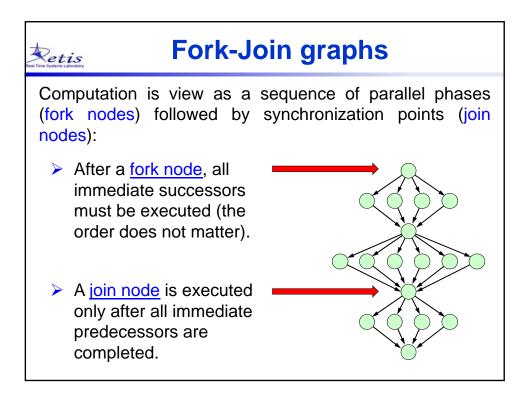

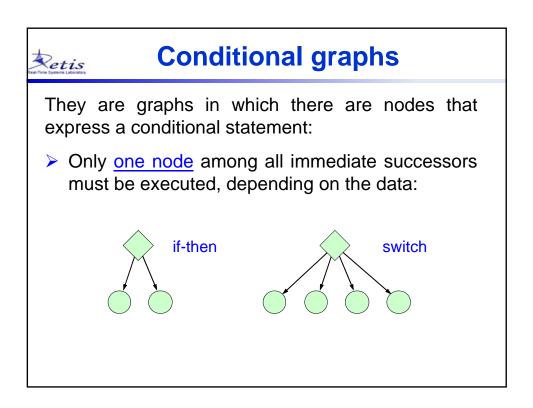

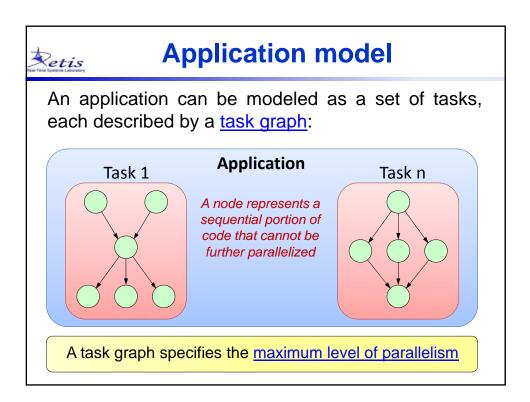

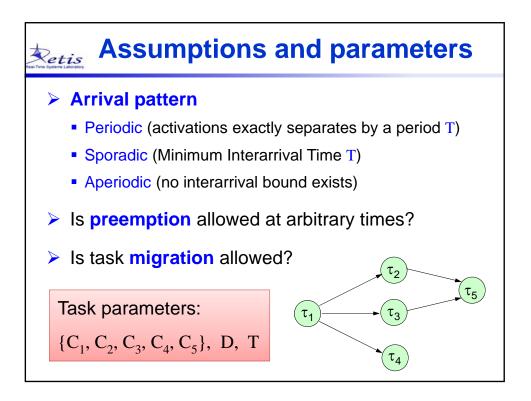

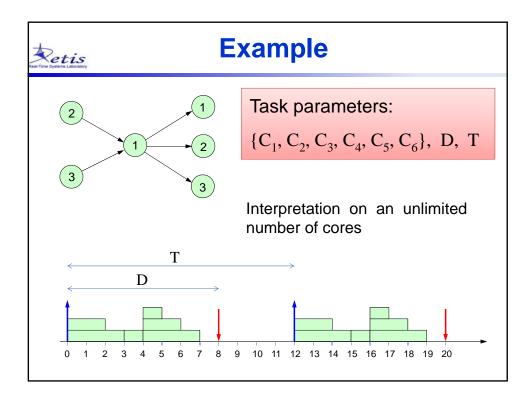

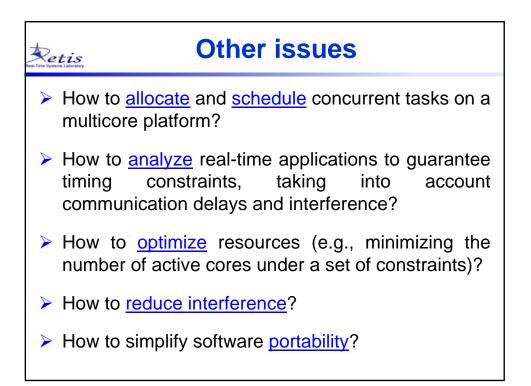

## How to exploit multiple cores? The efficient exploitation of multicore platforms poses a number of new problems that are still being addressed by the research community. When porting a real-time application from a single core to a multicore platform, the following key issues have to be addressed: How to split the code into parallel segments that can be executed simultaneously? How to allocate such segments to the different cores?

| Other problems                                                                                                                                                                                                                                |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

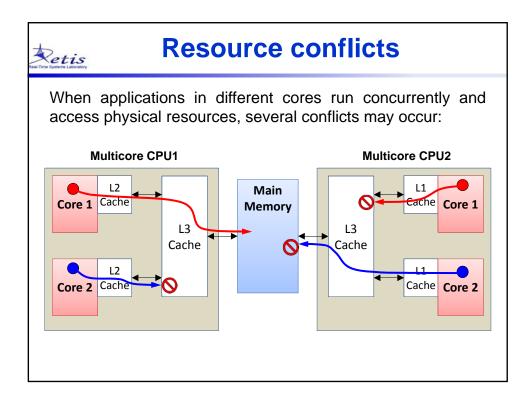

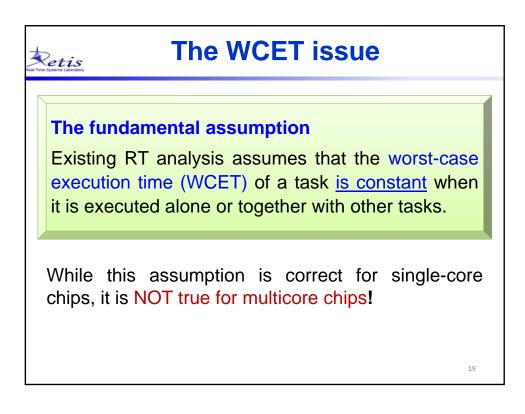

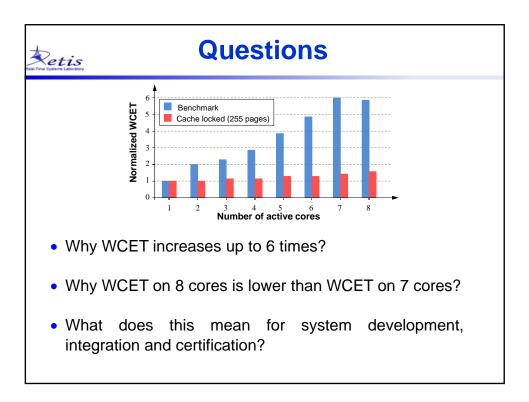

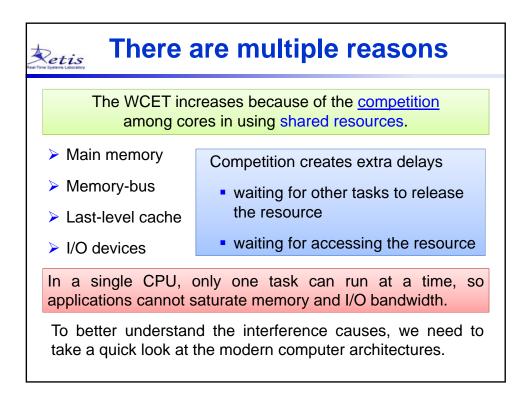

| In a single core system, concurrent tasks are sequentially executed on the processor, hence the access to physical resources is <u>implicitly serialized</u> (e.g., two tasks can never cause a contention for a simultaneous memory access). |  |  |  |  |

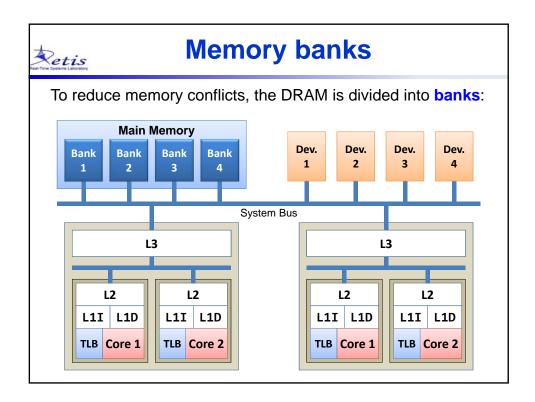

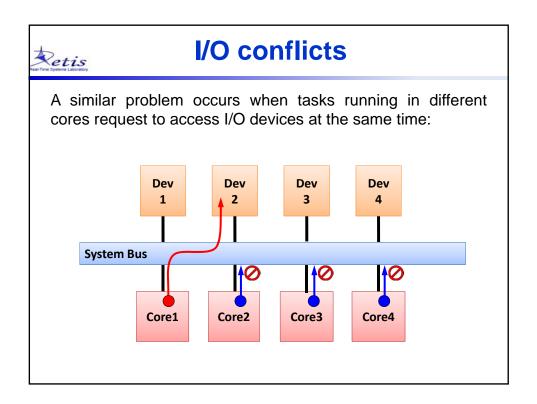

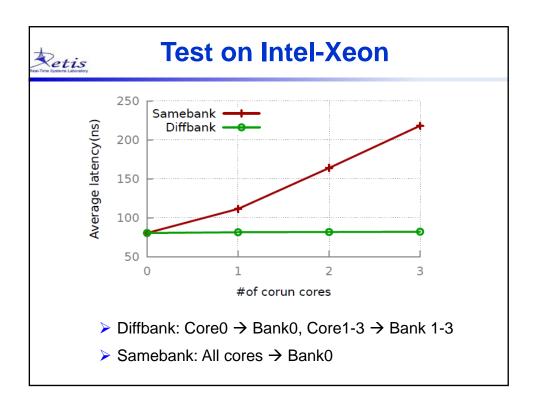

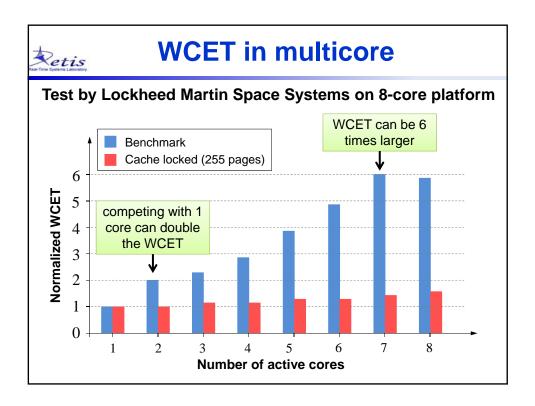

| In a multicore platform, different tasks can run simultaneously on different cores, hence several conflicts can arise while accessing physical resources.                                                                                     |  |  |  |  |

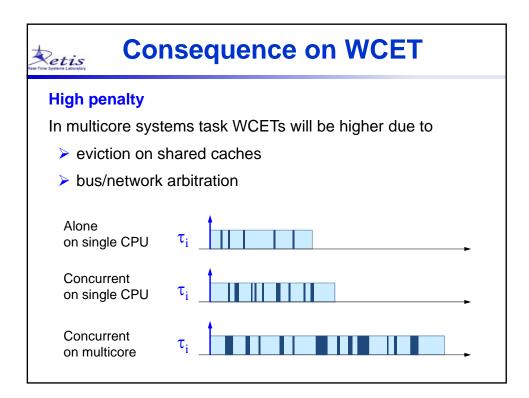

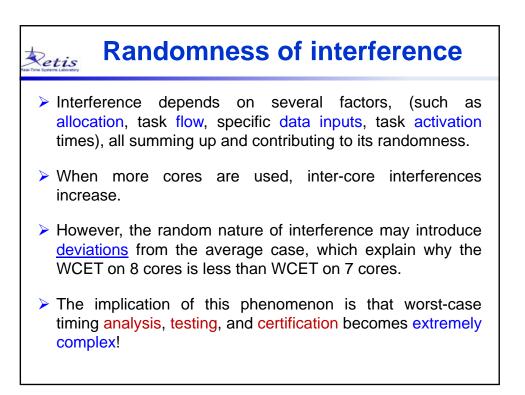

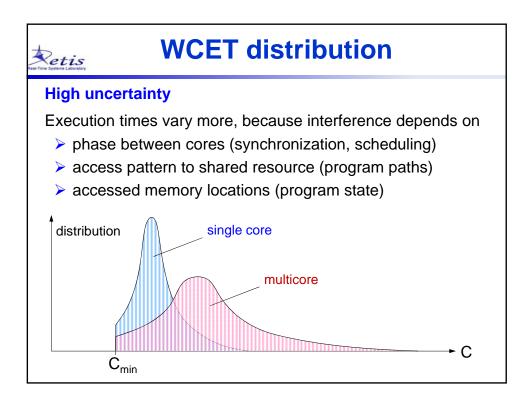

| Such conflicts not only introduce interference on task execution but also increase the Worst-Case Execution Time (WCET) of each tasks.                                                                                                        |  |  |  |  |

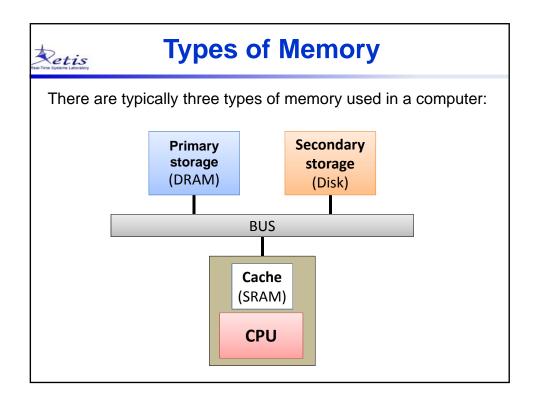

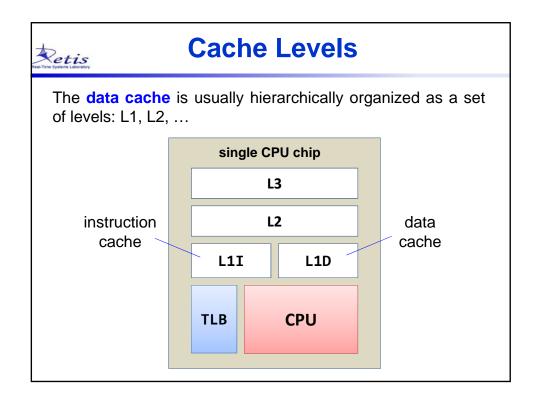

| Access times                   |         |          |              |  |

|--------------------------------|---------|----------|--------------|--|

|                                | latency | capacity | price per GB |  |

| Secondary Storage<br>(Disk)    | 12 ms   | 1 TB     | \$ 0.1       |  |

| Secondary<br>Storage Cache     | 50 μs   |          | x 100        |  |

| Main Memory                    | 120 ns  | 16 GB    | \$ 10        |  |

| L3 Cache                       | 80 ns   | 16 MB    | x 100        |  |

| L2 Cache                       | 20 ns   | 1 MB     |              |  |

| L1 Cache                       | 10 ns   | 64 KB    | \$ 1000      |  |

| CPU<br>Logic<br>Unit Registers | 1 ns    | 1 KB     |              |  |