# Energy Saving in Real-Time Embedded Systems

#### Anno Accademico 2013-2014

Corso di perfezionamento Innovative Technologies

# Energy Saving in Real-Time Embedded Systems

Autore

Mario Bambagini

Tutor

Giorgio Buttazzo

ISBN: XXXXXXXXXXXXX

#### **Abstract**

This thesis addresses the energy-aware scheduling issue in real-time embedded systems, while considering single-core, multi-core and distributed architectures.

In actual computational platforms, the energy consumption is rapidly growing due to the continuous technological improvements which let designers deploy far more transistors per inch, increasing the provided facilities. Besides the higher cost to power the electronic systems, the higher energy dissipation represents a serious design issue as such energy is transformed in heat which, if not effectively dissipated, may increase the probability of faults and shorten the overall lifetime.

In real-time systems, the data correctness does not depend only on the their values, but also on when they are produced. In other words, real-time schedulers are in charge of guaranteeing that jobs are successfully executed by their deadlines. Such time-critical systems are widely used in industry to increase the predictability and reliability, spreading from soft real-time systems (e.g.: video-conference software) where a deadline miss affects only the quality of service, to hard real-time systems (e.g.: flight controllers) in which consequences may be harmful.

Such a scenario introduces an interesting trade-off between time requirements associated to the workload execution and energy dissipation. On one hand, real-time applications require high performance to meet timing constraints. On the other hand, the energy is minimized by either lowering the performance level or switching the system off, which both lead to a delay in the workload execution. According to such assumptions, schedulers must judiciously grant the appropriate amount of computational resources to the pending workload in such a way their deadlines are guaranteed and the overall dissipation is reduced, at the same time.

Concerning single-core platforms, we proposed an innovative approach which, exploiting a different task model, significantly beats the state of the art. Then, the energy-saving problem is enhanced by considering bandwidth requirements which features sensor nodes and a scheduling algorithm is provided to handle it. In addition, the actual beliefs about the energy issue are pragmatically put in discussion and analyzed from a practical point of view.

Multi-core platforms have also been taken into account, providing an analysis of several partitioning heuristics.

Finally, the problem of partitioning a real-time workload on distributed systems was taken into account, dealing also with fault tolerance issues rather than only with real-time and energy constraints.

The analysis starts motivating the problem in Chapter 1, detailing the reasons behind the energy dissipation and introducing the actual solutions which aim at keeping it under control. Then, Chapter 2 considers the power and workload models which have been considered, whereas Chapter 3 reports the state-of-the-art algorithms which addressed the same problem. The analysis proceeds with the description of the proposed solutions for single-core, multi-core and distributed systems which are reported in Chapter 4, Chapter 5 and Chapter 6, respectively. In addition, Chapter 7 addresses the real-time scheduling issue for systems with renewable energy. Finally, Chapter 8 concludes the thesis remarking the main results.

## **Contents**

| 1 | Intr | oductio       | on                                                   | 3  |  |  |

|---|------|---------------|------------------------------------------------------|----|--|--|

|   | 1.1  | Energ         | y issue                                              | 4  |  |  |

|   | 1.2  | Energ         | y management systems                                 | 7  |  |  |

| 2 | Syst | ystem model 8 |                                                      |    |  |  |

|   | 2.1  | Power         | model                                                | 8  |  |  |

|   | 2.2  |               | oad model                                            | 12 |  |  |

| 3 | Rela | ited wo       | rk                                                   | 14 |  |  |

|   | 3.1  | Energ         | y-aware scheduling on single-core systems            | 14 |  |  |

|   |      | 3.1.1         | DVFS algorithms                                      | 15 |  |  |

|   |      | 3.1.2         | DPM algorithms                                       | 19 |  |  |

|   |      | 3.1.3         | Integrated DVFS-DPM algorithms                       | 20 |  |  |

|   | 3.2  | Energ         | y-aware scheduling on multi-core systems             | 22 |  |  |

|   |      | 3.2.1         | Homogeneous cores                                    | 23 |  |  |

|   |      | 3.2.2         | Heterogeneous cores                                  | 24 |  |  |

|   | 3.3  | Simila        | ar problems                                          | 25 |  |  |

|   |      | 3.3.1         | Energy harvesting                                    | 25 |  |  |

| 4 | Ene  | rgy-awa       | are scheduling on single-core systems                | 28 |  |  |

|   | 4.1  |               | y efficiency exploiting the Limited Preemptive model | 28 |  |  |

|   |      | 4.1.1         | System model                                         | 29 |  |  |

|   |      | 4.1.2         | Motivational examples                                | 30 |  |  |

|   |      | 4.1.3         | Background on limited preemption                     | 32 |  |  |

|   |      | 4.1.4         | Proposed approach                                    | 34 |  |  |

|   |      | 4.1.5         | Experimental results                                 | 37 |  |  |

|   | 4.2  | Energ         | y-aware co-scheduling of tasks and messages          | 42 |  |  |

|   |      | 4.2.1         | System model                                         | 42 |  |  |

|   |      | 4.2.2         | Background on schedulability analysis                | 44 |  |  |

|   |      | 4.2.3         | Proposed approach                                    | 44 |  |  |

|   |      | 4.2.4         | Experimental results                                 | 50 |  |  |

|   | 4.3  | Energ         | y-aware framework in tiny RTOS                       | 52 |  |  |

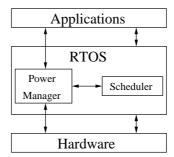

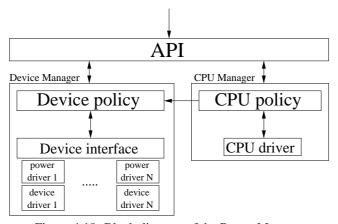

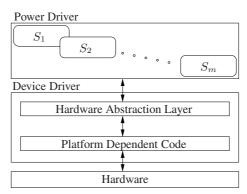

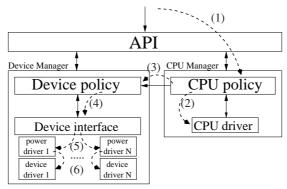

|   |      | 4.3.1         | Architecture                                         | 53 |  |  |

|   |      | 4.3.2         | Implemented policies                                 | 55 |  |  |

|   |      | 4.3.3         | Experimental results                                 | 58 |  |  |

|   | 4.4  | Algori        | ithm evaluation                                      | 61 |  |  |

|   |      | 4.4.1         | Limits of existing approaches                        | 62 |  |  |

|   |      | 442           | Measurements                                         | 63 |  |  |

|   |                                                | 4.4.3    | Experimental results                                     | 65  |  |

|---|------------------------------------------------|----------|----------------------------------------------------------|-----|--|

| 5 | Ene                                            | rgy-awa  | are scheduling on multi-core systems                     | 69  |  |

|   | 5.1                                            | Energy   | y-aware partitioning on homogeneous multi-core platforms | 69  |  |

|   |                                                | 5.1.1    | System model                                             | 70  |  |

|   |                                                | 5.1.2    | Heuristics                                               | 71  |  |

|   |                                                | 5.1.3    | Experimental results                                     | 72  |  |

| 6 | Energy-aware scheduling in distributed systems |          |                                                          |     |  |

|   | 6.1                                            | Energy   | y and bandwidth-aware co-allocation                      | 76  |  |

|   |                                                | 6.1.1    | System model                                             | 77  |  |

|   |                                                | 6.1.2    | Problem statement                                        | 80  |  |

|   |                                                | 6.1.3    | Proposed algorithms                                      | 83  |  |

|   |                                                | 6.1.4    | Experimental results                                     | 84  |  |

| 7 | Energy-aware scheduling with renewable energy  |          |                                                          |     |  |

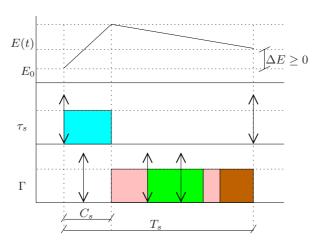

|   | 7.1                                            |          | n model                                                  | 88  |  |

|   |                                                | 7.1.1    | Power model                                              | 88  |  |

|   |                                                | 7.1.2    | Task model                                               | 89  |  |

|   | 7.2                                            | Propos   | sed approach                                             | 89  |  |

|   |                                                | 7.2.1    | Algorithm                                                | 91  |  |

|   |                                                | 7.2.2    | A sufficient condition for schedulability                | 93  |  |

|   |                                                | 7.2.3    | Enhancing the algorithm for mixed workloads              | 94  |  |

|   | 7.3                                            | Experi   | mental results                                           | 95  |  |

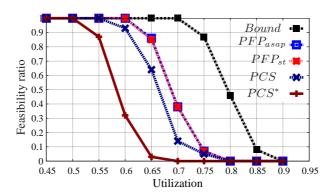

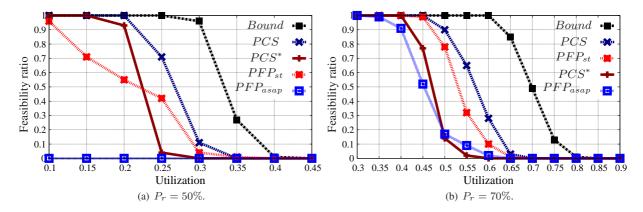

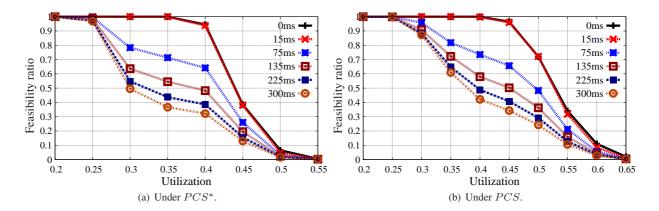

|   |                                                | 7.3.1    | Feasibility ratio                                        | 95  |  |

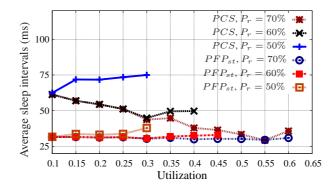

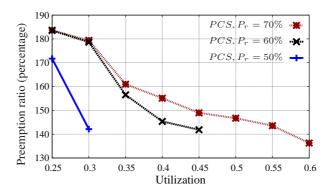

|   |                                                | 7.3.2    | Online metrics                                           | 97  |  |

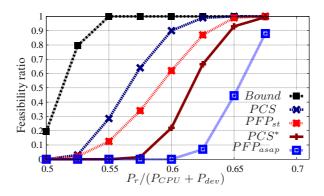

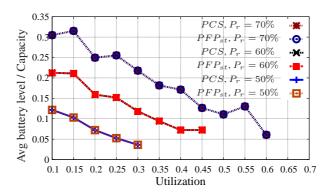

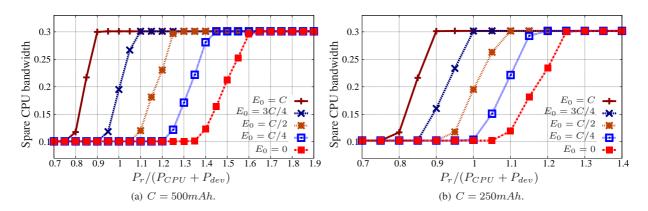

|   |                                                | 7.3.3    | Effective spare CPU bandwidth                            | 99  |  |

| Q | Con                                            | clucione | s.                                                       | 101 |  |

## **Chapter 1**

## Introduction

In the last decades, the *Information Technology* has grown exponentially and enhanced many fields, spreading from consumer electronics (e.g., desktops and notebooks) to specific sectors, such as embedded and high performance domains.

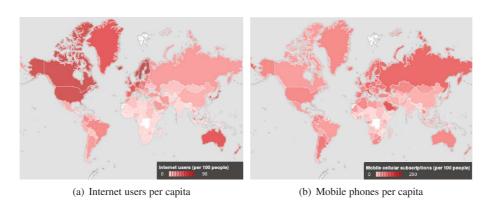

According to the data published by the World Bank [WBL] referred to the period 2009-2013, the numbers of internet users and mobile devices (represented in Figure 1.1(a) and Figure 1.1(b), respectively) have reached astonishing peaks in developed and BRIC countries. More precisely, in north America, the 96% of the population own an internet subscription and, in the eastern part of the world, almost three mobile devices belong to each person. Moreover, an interesting grown features also the developing countries, as such technologies represent a profitable market and an extraordinary tool for improving the quality of life.

Figure 1.1: World Bank statistics for the period 2009-2013.

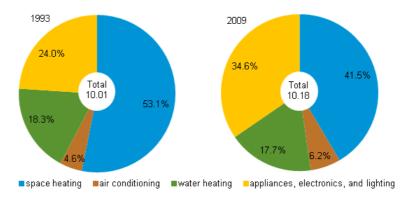

However, the previous numbers state only the actual facts. Scientists [Gat07,Gor13] agree unanimously on the fact that such trends are steadily growing and can not be stopped or even slowed down. Hence, we are part of a world whose energy demand will keep rising constantly regardless the development level of each country. In order to make such an aspect more clear, let us consider how the energy consumption has varied in the U.S. houses in almost 15 years, as reported by the Residential Energy Consumption Survey [REC] and depicted in Figure 1.2. The average consumption due

to electronics has rose up of an additional 10%, passing from 24% to 34.6%.

For such reasons and others, which are unfortunately out of the scope of this thesis, the energy consumption is a crucial point which must be effectively addressed in current systems. More precisely, this work focuses its attention on the real-time scheduling issue of systems in which the software execution is characterized from time constraints.

This chapter proceeds analyzing the problem from an engineering point of view, detailing the technical aspects which feature the energy dissipation (Section 1.1) and giving a glance at the actual solutions (section 1.2).

Figure 1.2: Results of the Residential Energy Consumption Survey.

#### 1.1 Energy issue

The most widespread electronic technology in actual digital circuits is CMOS (*Complementary Metal-Oxide Semiconductor*), whose peak power dissipation happens during the state transitions of the transistors.

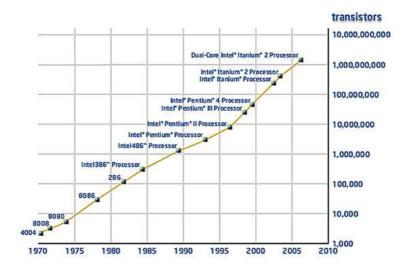

Intuitively, the higher the number of implemented features, the higher the number of transistors in the system and, consequently, the higher the power dissipation. In other words, a higher request of energy is the direct consequence of the increased performance. This is the side effect of the Moore's empiric law which states the growth of the number of transistors in the processors, as showed in Figure 1.3: *the number of transistors in a chip doubles every eight months*.

For such a reason, the frequency scaling feature has been introduced for enabling the application level to scale the performance down in order to reduce the transition rate and then, the consequent energy dissipation. Other techniques which are widely exploited at design time consists of implementing different physical parameters (such as supply and threshold voltage) to characterize particular circuits with less strict performance requirements. However, such techniques mainly concern design-time strategies which are out of the scope of this work.

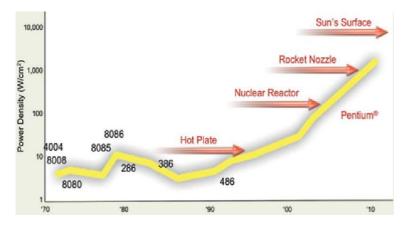

Another side effect of the increased power consumption is related to the fact that most power is converted in heat which must be effectively dissipated. The trend of heat density is depicted in Figure 1.4, representing the not easy task which designers have to deal with. Besides the intuitive drawback of physically dissipating such heat by appropriate cooling systems, high temperatures drastically reduces performance (scattering effect), leading to the infamous *power wall*. In other words, it represented a stall

Figure 1.3: Moore's law about the transistor number in processors.

point in which any attempt to improve performance by either adding more transistors or increasing the frequency, caused an overall powerfulness reduction.

Figure 1.4: Heat density in Intel single-core processors.

Along with the memory and ILP walls, such limitations led to the adoption of multi-core systems. In such architectures, although cores run at lower frequencies, the overall performance is boosted up by the parallel execution of threads.

However, single-core systems are still widely used in the embedded system domain which generally requires lower performance but higher predictability and reliability.

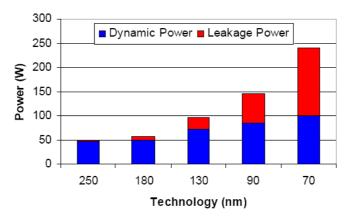

As a consequence of progresses in the VLSI manufacturing, miniaturization has considerably shrunk the transistor size, lowering the supply voltage, thereby reducing the dynamic power consumption. Although the threshold voltage has also been lowered, the gap between supply and threshold voltages was reduced. This led to a significant increase in the leakage consumption, because the smaller the gap, the higher

Figure 1.5: Dynamic and leakage dissipation for different technology processes.

the sub-threshold dissipation [SPG02, NC10, KSH02]. Thus, the static power consumption, whose contribution was considered negligible, has become as important as the dynamic power. More precisely, the leakage consumption is ascribable to quantum phenomenons and it is always present, not depending on the system activity. Figure 1.5 reports the contribution of the leakage and dynamic dissipation for different technology processes in Intel [INT] CPUs, remarking the rising impact of the static consumption.

To address such an issue, several low-power states have been introduced to let the system reduce the power dissipation when there is no workload to execute. More precisely, such states suspend the code execution and switch off several components of the system: the more components are disabled, the lower the power consumption. However, the required time to enter and exit the low-power state depends on the number and kind of asleep components, which may introduce conflicts with the time requirements of the applications. For such a reason, actual processors provide a wide range of low-power states, characterized from different consumption and overhead.

Figure 1.6: Growth of battery capacity in 20 years.

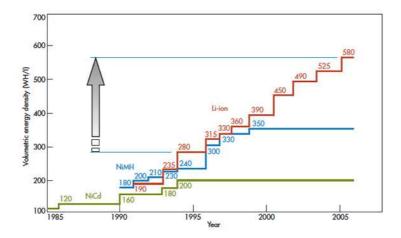

The last note, but not least, is related to the gap between required and supplied power for battery-operated platforms. Within a certain margin of approximation, we can assert that the power consumption broadly doubles every eighteen months as a consequence of the Moore's law, however, the battery capacity doubles every ten years, as highlighted in Figure 7.11. In other words, two different improving paces feature power suppliers and consumers, leading to a gap which should be addressed by software or by other mechanisms.

#### 1.2 Energy management systems

Nowadays, many end-user and specific-purpose processors provide hardware facilities which attempt to automatically reduce the power dissipation through frequency throttling and low-power states, such as Intel's *SpeedStep* and AMD's *PowerNow!* [AMD].

However, much effort has been profused to address the problem at a more abstract layer in order to implement strategies which are hardware independent.

The first attempt to keep energy consumption under control was Advanced Power Management (APM), introduced in the 1992 by Intel and Microsoft [MIC]. The main purpose consisted of increasing the battery duration in notebooks which started to become popular in that period. The component allows APM-aware applications to communicate their energy requirements to the APM-driver provided by the operating system. The requests are subsequently supplied to the APM-aware BIOS, in charge of managing the APM-compliant hardware. The main drawback of this approach is that figuring out and requesting a specific power management policy from the operating system becomes essentially a responsibility of the application – ideally power management should be transparent to the individual applications. However, one of its most important contribution was the introduction of APM-compliant hardware to support a set of different states with specific power consumption and functionality features.

In 1996, Intel, Microsoft, and Toshiba [TOS] released an enhanced framework, called *Advanced Configuration and Power Interface* (ACPI), which has became the standard de facto for device configuration and monitoring. In particular, ACPI offers the operating system (in charge of handling the settings and power state transitions) an easy and flexible interface to discover and configure the compliant devices. The main contribution consists of having moved the policies from the application level to the operating systems (OSPM - Operating System Power Management), implementing a better abstraction. For instance, unused system components, as well as the entire system, can be switched to a low-power state, according to the current state and user preferences transparently to the running processes.

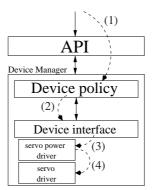

Despite the ACPI approach is very flexible and effective for many general purpose systems, it is considerably expensive in terms of computation and memory requirements for small footprint systems. For such a reason, in the embedded systems domain, the problem is mostly addressed in a tailored way in order to deal with the limited resources. However, Brock and Rajamani [BR03] proposed a solution with a set of pre-defined policies. The tasks are divided into groups according to either their energy requirements or importance classes. The current policy is chosen by the *policy manager*, a component provided by the system designer. The system behavior is encoded as a grid, where each cell represents the configuration to be adopted when a task of a specific group runs on the processor and a policy is active.

## **Chapter 2**

## System model

This section presents the most relevant models used in the literature for the design and analysis of energy-aware scheduling algorithms. Specifically, Section 2.1 overviews various power models, and Section 2.2 presents the computational workload models.

#### 2.1 Power model

The power consumption of a single gate in CMOS technology has been modeled accurately in the literature [CSB95]. Specifically, the power consumption  $P_{gate}$  of a gate is expressed as a function of the supply voltage V and clock frequency f:

$$P_{qate} = p_s C_L V^2 f + p_s V I_{short} + V I_{leak}$$

(2.1)

where  $C_L$  is the total capacitance driven by the gate,  $p_s$  is the gate activity factor (i.e., the probability of gate switching),  $I_{short}$  is the current between the supply voltage and ground during gate switching, and  $I_{leak}$  is the leakage current, which is independent of the actual frequency and system activity. The three components of the sum in Equation (2.1) correspond to *dynamic*, *short circuit* and *static* power components, respectively.

In essence, the dynamic power is the power required to load and unload the output capacitors of the gates. Unlike the dynamic component, the short circuit current  $I_{short}$  depends on the temperature, size, and process technology. The leakage current is a quantum phenomenon where mobile charge carriers (electrons or holes) pass by tunnel effect through an insulating region, leading to a current that is independent from switching activity and frequency. Such a dissipation is due to three causes: gate leakage (from gate to source losses), drain junction leakage (losses in the junctions) and subthreshold current (from drain to source losses).

In Equation (2.1), the two variables that do not depend on the physical parameters are the supply voltage V and the clock frequency f. However, they are not completely independent, because the voltage level limits the highest frequency that can be used: the lower the voltage, the higher the circuit delay. Specifically, the circuit delay is related to the supply voltage V by the following equation:

$$circuit \ delay = \frac{V}{(V - V_T)^2} \tag{2.2}$$

where  $V_T$  denotes the *threshold voltage*, which is defined as the minimum voltage needed to create a channel from drain to source in a MOSFET transistor.

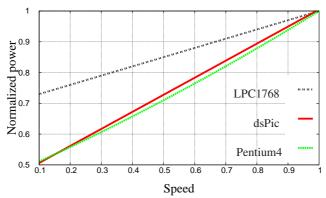

In the literature, the processor is assumed to be able to dynamically scale the clock frequency f in a given range  $[f_{min}, f_{max}]$ . Often, the analysis is performed by replacing the clock frequency by the processor  $speed\ s$ , defined as the normalized frequency  $s=f/f_{max}$ , so that the maximum processor speed is considered as  $s_{max}=1.0$ . In the existing work, we observe two main approaches: in one research line, the frequency/speed range is assumed to be of fine granularity; i.e., the system's frequency is considered continuous. As opposed to this ideal model, the second research line considers m discrete speed/frequency levels. This line is based on the observation that the current processors offer typically a small number of discrete speed levels.

To characterize the power consumption P(s) of the single-core system as a function of the processor speed, one of the most general formulations has been proposed by Martin and Siewiorek [MS01]:

$$P(s) = K_3 s^3 + K_2 s^2 + K_1 s + K_0. (2.3)$$

The  $K_3$  coefficient expresses the weight of the power consumption components that vary with both voltage and frequency. The second order term  $(K_2)$  captures the non-linearity of DC-DC regulators in the range of the output voltage. The  $K_1$  coefficient is related to the hardware components that can only vary the clock frequency (but not the voltage). Finally,  $K_0$  represents the power consumed by the components that are not affected by the processor speed.

Another variant of Equation (2.3) used in literature (e.g., [ZA09b]), is

$$P(s) = P_{ind} + P_{dyn}(s) \tag{2.4}$$

where the power dissipation is explicitly divided into static  $(P_{ind})$  and dynamic  $(P_{dyn}(s))$  power components.  $P_{ind}$  is assumed to be independent of the system speed, and  $P_{dyn}$  is assumed to be a polynomial function of the speed s.

A more specific power model (e.g., [BBL09]) considers the set of operating modes supported by the processor. Each mode is described by three parameters: the frequency f, the lowest voltage V that supports that frequency level, and the corresponding power consumption. To some extent, Martin's equation can be considered a generalization of this model, as it provides an interpolation of the various operating points on an ideal processor where the speed/voltage can be adjusted in a continuous manner.

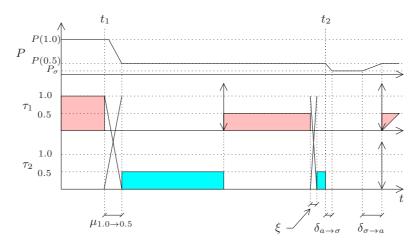

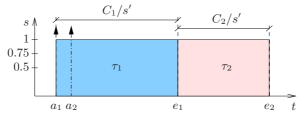

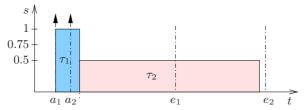

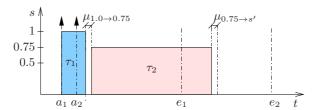

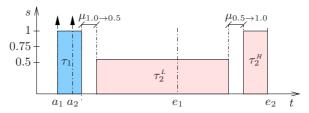

Switching from one speed level to another involves both a *time* and *energy* overhead. These overheads depend both on the original and final speed levels (e.g., [XMM07, MHQ07]). When scaling the speed, the execution is suspended and the overhead is mostly due to the time required to switch the crystal on and/or adjusting the Phase-Locked Loop (PLL). Generally, the wider the difference between the two frequencies, the higher the introduced overhead. In this work, the notation  $\mu_{s_1 \to s_2}$  denotes the time overhead when transitioning from the speed level  $s_1$  to the speed level  $s_2$ .

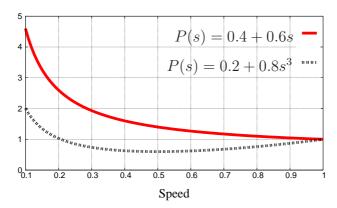

When the leakage power dissipation is not negligible (i.e.,  $K_0 \neq 0$  and  $P_{ind} \neq 0$  in Equation (2.3) and Equation (2.4), respectively), scaling the system speed down also increases the computation times and leakage energy consumption, which in turn may increase the total energy consumption. To address this issue, the concept of critical speed (also known as the energy-efficient speed), denoted by  $s^*$ , was introduced to denote the lowest available speed that minimizes the total energy consumption, which consists of dynamic and static power figures (e.g., [ADZ06,CK06]). Specifically, if we assume P(s) as in Equation (2.3), it becomes strictly convex, and  $s^*$  is defined as the

Figure 2.1:  $\frac{\delta P(s)/s}{\delta s}$  function of DPM- and DVFS-sensitive models.

lowest speed that minimizes the energy consumption per cycle, which is equivalent to the speed value that makes the derivative of P(s)/s null.

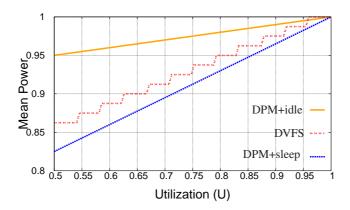

For instance, let us consider the power function  $P(s) = 0.2 + 0.8s^3$ . The derivative of P(s)/s is  $\frac{\delta P(s)/s}{\delta s} = 1.6s - 0.2/s^2$  which is null for  $s = s^* = 0.5$ , implying that, scaling the speed below 0.5 is not energy-efficient. This can be easily shown by considering a task with WCET = 10 time units while assuming that it can be executed at any speed  $\in \{0.2, 0.5, 0.7, 1.0\}$  without missing its deadline. The relative energy consumptions for executing the task at the different speed assignments are: E(0.2) = P(0.2) \* 10/0.2 = 10.32, E(0.5) = P(0.5) \* 10/0.5 = 6, E(0.7) = P(0.7) \* 10/0.7 = 6.8 and E(1.0) = P(1.0) \* 10 = 10. The minimum energy consumption is indeed obtained for  $s^*$ , while it increases at both lower and higher speeds. One can see that the energy consumption of a task is a quadratic function with global minimum at  $s^*$ . A model whose critical speed is lower than the maximum one is identified as DVFS-sensitive, whereas a DPM-sensitive architecture is characterized by  $s^* = 1.0$ . Figure 2.1 shows the  $\frac{\delta P(s)/s}{\delta s}$  function of the previously considered model  $(P(s) = 0.2 + 0.8s^3)$  in contrast with a DPM-sensitive model (P(s) = 0.4 + 0.6s). It is worth noting that such an analysis minimizes only the energy consumption during the time intervals when tasks are executed, because it implicitly assumes a negligible power consumption during the CPU idle intervals.

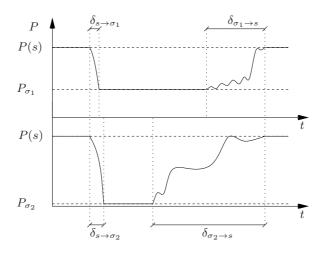

An additional feature provided by almost all the current processors is the ability to switch to low-power states when the task execution is suspended. Each low-power state  $\sigma_x$  is characterized by its power consumption  $(P_{\sigma_x})$  and the time and energy overheads involved in entering and exiting that state, denoted as  $\delta_{s\to x},\,\delta_{s\to x},\,E_{s\to x}$  and  $E_{x\to s},$  respectively. For the sake of simplicity, we use the overall time and energy overheads associated with the low-power state  $\sigma_x$ , namely  $\delta_{\sigma_x}$  and  $E_{\sigma_x}$ , as the sum of the initial and final transition overheads. In general, the "deeper" a low-power state, the lower the power consumption, but also the higher time and energy overheads involved in the transition. An exhaustive analysis of the low-power states in actual architectures has been undertaken by Benini et al. [BBDM00].

Considering the time and energy overheads involved in transitions to low-power states, there is, in general, a minimum time interval that justifies switching to a specific low-power state – this is because, if the system returns to active state too quickly, the energy overhead of the transition would offset the power savings of the low-power state. Consequently, the parameter  $B_{\sigma_x}$ , referred to as the *break-even time*, corresponds to the

Figure 2.2: An example with two low-power states.

length of the shortest idle interval that must be available in the schedule to effectively exploit the sleep state  $\sigma_x$ . Specifically,  $B_{\sigma_x}$  is the maximum of the time required to perform a complete transition and the minimum idle time length that can amortize the switching energy (e.g., [QNHM04, ZA09a]):

$$B_{\sigma_x} = \max\left(\delta_{\sigma_x}, \frac{E_{\sigma_x} - \delta_{\sigma_x} \cdot P_{\sigma_x}}{P_{ref} - P_{\sigma_x}}\right)$$

(2.5)

where  $P_{ref}$  is the power consumption of the processor in a default state when tasks do not execute. For instance,  $P_{ref}$  can be the power consumption of a particular inactive state which requires a negligible transition overhead, or, in case the processor is kept active during idle intervals, it may correspond to the power consumption at the minimum speed level.

Different low-power states are characterized by different parameters. Figure 2.2 illustrates two different state transitions. The first case illustrates a low-power state  $\sigma_1$  with a medium power consumption and a relatively short break-even time. On the other hand, the second low-power state  $\sigma_2$  guarantees the lowest power consumption but introduces a significant temporal overhead from active to sleep and back to active. Finding the most suitable low-power state depends on the length of the available idle interval which, in turn, is determined by the timing constraints.

When multi-core processors are considered, the overall power consumption is function of the particular state and speed of each core. More precisely, the energy consumption of the entire system in the interval  $[t_1, t_2]$  can be expressed as:

$$E(t_2, t_1) = E_{CPU}(t_2, t_1) + E_{NO\_CPU}(t_2, t_1).$$

(2.6)

where  $E_{CPU}$  denotes the energy dissipated by the processors and  $E_{NO\_CPU}$  the energy dissipated by the remaining components, including the main memory, disks, network interfaces and other peripherals whose behaviors can be considered not directly affected by the running frequency of the processors. Although running tasks impact on such devices, for the sake of simplicity, we assume a constant average device dissipation, that is:

$$E_{NO\_CPU}(t_2, t_1) = (t_2 - t_1) \cdot P_{NO\_CPU},$$

where  $P_{NO\_CPU}$  is the power consumed by the devices. In other papers,  $P_{NO\_CPU}$  is also referred to as  $P_{uncore}$ . Since each processor can have a different state/speed at any time, the processor energy dissipation is the integral of power consumption in the interval  $[t_1, t_2]$ :

$$E_{CPU}(t_2, t_1) = \sum_{j} \int_{t_1}^{t_2} P_{CPU_j}(t) dt.$$

Basically, the processor power consumption at time t is a function of the actual state of each processor: the low-power state in use if it is asleep, or the running speed if active.

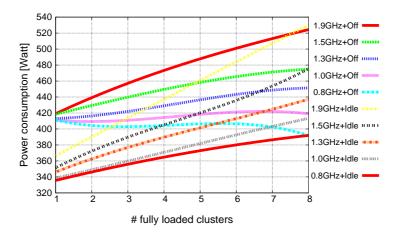

To characterize the power model of the processors, the equations concerning the active power consumption (Equation (2.3) and Equation (2.4)) can be extended to handle m different variables for each core (e.g., [CH14]). However, considering the scenario in which several cores are put in one of the low-power state while the remaining units are active is not representable with the previous approach. In order to provide a representation for such configurations, an effective solution, in spite of its simplicity, consists of tabling the power dissipation for a subset of all the possible scenarios (e.g., [BBB13]).

#### 2.2 Workload model

In hard real-time systems, the computational workload is typically characterized by a set  $\Gamma$  of n periodic or sporadic tasks  $\{\tau_1, \tau_2, ..., \tau_n\}$ . Each task  $\tau_i$  is cyclically activated on different input data and therefore generates a potentially infinite sequence of instances  $\tau_{i,1}, \tau_{i,2}, \ldots$ , referred to as jobs. The jobs of a periodic task  $\tau_i$  are regularly separated by a period  $T_i$ , so the release time of a generic job  $\tau_{i,k}$  can be computed as

$$r_{i,k} = \Phi_i + (k-1)T_i$$

where  $\Phi_i$  denotes the activation time of the first job, also referred to as the *task offset*. On the other hand, in the case of *sporadic* task  $\tau_i$ , the period  $T_i$  indicates the *minimum inter-arrival time* of its jobs:  $r_{i,k+1} \geq r_{i,k} + T_i \ \forall k$ . A real-time task  $\tau_i$  is also characterized by a *relative deadline*  $D_i$ , which specifies the maximum time interval (relative to its release time) within which the job should complete. Depending on the specific assumptions, relative deadlines can be less than, equal to, or greater than periods. In the most common case, the relative deadlines are equal to periods, which is commonly called as *implicit-deadline task sets*. Once a job  $\tau_{i,k}$  is activated, the time at which it should finish its execution is called the *absolute deadline* and is given by  $d_{i,k} = r_{i,k} + D_i$ .

Each task  $\tau_i$  is also characterized by a Worst-Case Execution Time (WCET)  $C_i(s)$ , which is a function of the processor speed. In a large body of works, WCET is considered to be fully scalable with the speed, i.e.,  $C_i(s) = C_i/s$ . However, a number of research works (e.g., [SAMR03, ADZ06]) noted that this is only an upper bound, because several I/O and memory operations are performed on devices and memory units that do not share the clock frequency with the CPU. For instance, if a task moves data to/from hard disk drive, the operation depends mostly on the bus clock frequency, the hard disk reading/writing speed, and the interference caused by other tasks accessing to the bus. To take the speed-independent operations into account, the task's WCET can be split into a fixed portion  $C_i^{fix}$  not affected by speed changes and a variable portion  $C_i^{var}$  which is fully scalable with the speed. Hence,

$$C_i(s) = C_i^{fix} + C_i^{var}/s.$$

Figure 2.3: An example task schedule and corresponding power consumption.

An equivalent representation (e.g., [BBMB13a]) which is often used to model such feature is

$$C_i(s) = \alpha C_i^{max} + (1 - \alpha) C_i^{max} / s,$$

where  $C_i^{max}$  is the overall execution time at the maximum speed ( $C_i^{max}=C_i(1.0)=C_i^{fix}+C_i^{var}$ ) and  $\alpha=C_i^{fix}/C_i^{max}$  is the fraction of speed-independent code.

In terms of CPU scheduling, tasks may be assigned a *fixed-priority* level, representing the relative importance or urgency of the task with respect to the others. In systems with dynamic priorities, the priority levels of jobs of a given task may vary over time: for instance, with the *Earliest-Deadline-First* (EDF) policy [LL73], the priorities are determined according to the absolute deadlines of the current active jobs of the periodic tasks, and hence, naturally vary over time.

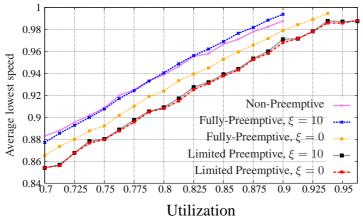

In most algorithms, tasks are assumed to be fully *preemptive*, meaning that they can be suspended at arbitrary points in favor of higher-priority tasks. Preemption simplifies the schedulability analysis, but introduces a runtime overhead  $\xi$  (preemption cost) during task execution, which includes several penalties such as the context switch cost, the pipeline invalidation delay, and the cache-related preemption delay. The preemption cost is often assumed to be constant and speed independent. On the other hand, *non-preemptive scheduling*, while characterized by negligible runtime overhead, introduces significant blocking delays on high priority tasks that heavily penalize schedulability.

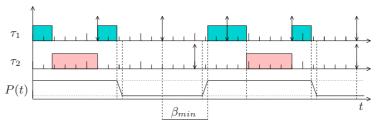

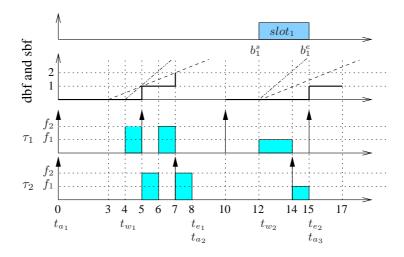

To visualize the power consumed during task execution, the scheduling diagram is typically extended by representing the power consumed by a task on the vertical axis. Consequently, the total energy  $E(t_a,t_b)$  consumed by a task in an interval  $[t_a,t_b]$ , which is the integral of the power function during the interval, is given by the corresponding execution area. Figure 2.3 illustrates the schedule of two tasks where, at time  $t_1$ , the speed is changed from 1 to 0.5, and at time  $t_2$  the processor enters a sleep state. The speed scaling overhead  $\mu_{1.0\to0.5}$  and the preemption cost  $\xi$  are also shown in the diagram.

## **Chapter 3**

### **Related work**

This section introduces the most relevant algorithms which have addressed the energy-aware scheduling issue in real-time systems.

Several surveys on energy-aware scheduling have been published recently, their primary focus was on DVFS algorithms. For instance, Chen and Kuo [CK07] addressed single and multi-core systems, by classifying algorithms according to the task periodicity. Similarly, Kim [Kim06] surveyed the intra- and inter-task DVFS algorithms, by considering only single-core systems. Saha and Ravindran [SR12] reported a performance comparison of a number of single-core DVFS algorithms through their implementation in the GNU/Linux kernel [LIN]. More recently, [Mit14] has presented a general survey of energy management techniques for embedded systems, including also micro-architectural techniques. As an effort to provide a greater in-depth overview of the existing DVFS- and DPM-based algorithms, we surveyed in [BAB14] the most relevant energy-aware scheduling algorithms, focusing our research only on single-core systems.

This section broadly divides the algorithms in a first group which considers single-core platforms and a second one which deals with multi-core architectures. These two classes are presented in Section 3.1 and Section 3.2, respectively. A taxonomy is proposed for each group to further catalog algorithms and make the analysis easier. In addition, Section 3.3 reports several problems which are related to the energy awareness in real-time systems.

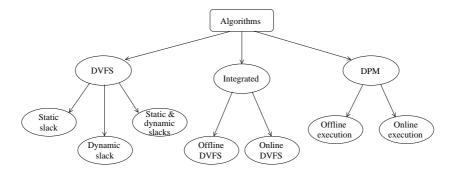

#### 3.1 Energy-aware scheduling on single-core systems

This section considers energy-aware real-time scheduling algorithms for single-core systems which are organized according to the taxonomy illustrated in Figure 3.1. The algorithms are first classified along the DVFS and DPM dimensions, based on the primary power management technique that they use. The DVFS algorithms (Section 3.1.1) are then divided according to the type of *slack* (the unused CPU time) that they reclaim for scaling speed to save energy: *static, dynamic,* or *both.* Specifically, the algorithms that exploit only the *static slack* consider the residual processor utilization in the worst-case execution, whereas those that reclaim the *dynamic slack* take advantage of the difference between the worst-case and the actual execution time of the jobs. In other words, the DVFS algorithms that exploit the dynamic slack take advantage of the runtime variability of the workload, since in practice many real-time jobs complete

Figure 3.1: Algorithm taxonomy for single-core systems.

early (i.e., without presenting their worst-case workload).

Such a classification does not immediately apply to DPM algorithms (Section 3.1.2), since, due to their work-conservative nature, the dynamic slack is automatically accounted in almost all the cases. Thus, they are classified as *offline* and *online* approaches.

Finally, the algorithms that use both DVFS and DPM techniques are designated as *integrated* algorithms (Section 3.1.3). These algorithms are further divided according to when the speed assignment decisions are made, either *offline* or *online*.

#### 3.1.1 DVFS algorithms

The DVFS-based algorithms rely on the system's capability of adjusting the processor supply voltage and frequency (hence, the speed) to reduce the power consumption, while still meeting the real-time constraints. Historically, such speed scaling techniques have been the first approach to face the energy management challenge, as in CMOS circuits the dynamic power consumption was recognized to be much more important than the leakage (static) consumption.

Most of the early DVFS algorithms have assumed a power function equal to  $P(s) = s^{\alpha}$  ( $2 \le \alpha \le 3$ ), implicitly ignoring the leakage power. Using such a power function, the lower the speed, the lower the consumed energy; hence, this power model favors the algorithms that use the lowest speed that can still meet the deadlines, leaving no idle intervals in the schedule.

The slack of a job refers to the CPU time that it does not use before its deadline. Hence, the *static slack* available to any job of a task  $\tau_i$  can be computed offline as  $slack_i = D_i - R_i$ , where  $R_i$  is the worst-case response time of  $\tau_i$ . At runtime, extra slack (referred to as *dynamic slack*) may become available when the job completes early, without consuming its WCET.

The DVFS solutions can be also classified as *inter-task* and *intra-task* algorithms. In inter-task algorithms, when a job is dispatched, it is guaranteed to execute at the same speed level until it completes or is preempted by another (high-priority) job. When it resumes execution (after preemption), the scheduler may re-adjust its speed by considering the available slack at that time. The *inter-task* algorithms form the majority of the current DVFS solutions, as it requires only the information about the WCET of the jobs, and involves low run-time overhead. On the other hand, if the information about the execution time of the job is available, in particular its *probability distribution*, then there may be benefits in adjusting the job's speed *while* it is in

progress, at well-determined points. This is the main idea behind the *intra-task* algorithms [XXMM04,XMM05,SKL01], in which the job starts to execute at a low speed level (relying on the fact that its early completion is more likely than the worst-case scenario), and then its speed is increased *gradually* at well-determined *power management points* (*PMPs*) as it continues to execute. Thus, for each task, a *speed schedule* is computed offline, showing what speed level will be assigned to its jobs during their execution, and at what point. The intra-task algorithms aim at minimizing the *expected dynamic energy consumption*, however they also require that the compiler generates code to enable the application to make system calls to the operating system at the well-determined PMPs during job execution, and they involve more overhead due to more frequent speed changes.

The rest of this section provides an overview of the most relevant DVFS algorithms, divided according to the type slack they exploit for scaling speed: static slack, dynamic slack or both.

#### Static slack reclaiming

One of the first papers on DVFS based energy-aware scheduling is proposed by Yao et al. [YDS95]. The paper presented three algorithms by considering aperiodic tasks, continuous CPU speed, no speed scaling overhead, negligible power consumption during idle intervals, and task computation times inversely proportional to CPU speed (C(s) = C/s). The first algorithm consists of recursive identification of time intervals with maximum computational density (defined as the sum of CPU cycles of the tasks with arrival and deadline within the interval, divided by the length of the interval length). Specifically, the algorithm identifies the interval with the maximum intensity, sets the CPU speed to the intensity value for that interval, and it is recursively re-invoked for the remaining execution intervals in the schedule. The offline algorithm is proved to be optimal and has an  $O(n \log^2 n)$  complexity for n aperiodic jobs. A second algorithm, executed online, considers jobs that may arrive dynamically. The algorithm recomputes the optimal schedule at each arrival time considering only the new and pending jobs. The third algorithm (AVR) sets the speed, for each instant, equal to the sum of density of those jobs whose arrival and deadline range contains the time instant under consideration. Although the complexity of AVR is lower than the previous optimal approaches, deadline misses may occur. In fact, since the speed is set equal to the sum of the worst-case utilization of the active jobs, the processor can be significantly slowed down when there are few active tasks, so the system may not be able finish the remaining work if additional tasks arrive, leading to deadline misses.

Ishihara and Yasuura [IY98] provided an analysis for synchronous frame-based real-time tasks (with identical release time and period), proving that under their assumed system model (no overhead and all tasks consume the same amount of energy), the energy is minimized when each job completes just at its respective deadline. That result implies that on a system with continuous speed/voltage, the total energy is minimized at the speed/voltage that reduces the idle time to zero. While that result is also implicit in the optimal [YDS95] algorithm mentioned above, the main contribution of [IY98] is the derivation of an important property of the systems with discrete speed levels: when the system is constrained to use a finite set of speed/voltage, the energy is minimized by using the two speed/voltage values adjacent to the speed value that is optimal assuming a continuous range. When systems where tasks may have different power consumption characteristics are considered, an immediate result is that using a uniform speed across all tasks is longer optimal, and there is a need to adjust the CPU

speed at context switch times. In two of the earliest efforts,

The problem of finding an optimal solution on a system with discrete speed levels was discussed in [BBL09], for a set of periodic or sporadic tasks under both EDF and Fixed-Priority (FP) scheduling policies. The authors provided a method to compute the optimal speed offline (first assuming a continuous speed spectrum) and then introduced a speed modulation technique to achieve the target speed using two discrete values. The analysis selects the pair of available frequencies that minimize the energy consumption by also incorporating time and energy switching overheads. The execution time consists of a part that is speed-dependent and another one which is not.

#### Dynamic slack reclaiming

All the algorithms considered here are based on EDF and assume that the computational times scale linearly with the speed (C(s) = C/s).

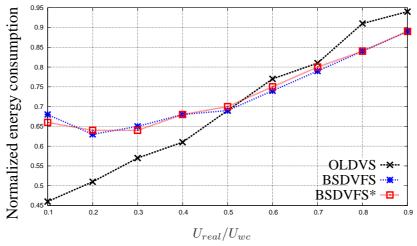

Lee and Shin [LS04] proposed OLDVS, an algorithm which accumulates the dynamic slack due to early completions and exploits it to decrease the CPU speed so that the current task is completed at the same time that it would complete in the schedule with the worst-case workload. The idea was improved in [GSL07] through the intratask algorithm OLDVS\*, which divides each job execution in two parts: the first part is executed at a low speed level and the speed is increased if does not complete by the end of the first part. This approach relies on the observation that the probability of completing the job in the first part is significantly higher than finishing in the second half. Both algorithms assume a discrete set of speeds, negligible power consumption during the idle intervals, and zero switching overhead.

Zhu et al. [ZM05] combined the DVFS mechanism with feedback control theory to save energy for periodic real-time task sets with uncertain execution times. Their approach uses a PID controller to compute the estimated execution time of the next job as a function of the difference between the actual and the expected execution time of the previous job of the same task. The plant in the closed control loop is represented by the EDF scheduler. The frequency/voltage selection is greedy, as it considers the estimated execution time for the running task and WCET for the others. Moreover, the frequency spectrum is assumed to be continuous and the speed scaling overhead is considered negligible. It is also assumed that the CPU uses the lowest speed level during the idle intervals.

Lawitzky et al. [LSP08] implemented an energy saving algorithm based on the Rate-Based Earliest Deadline (RBED) framework [BBLB03], which supports CPU time budget allocation and dispatching. The paper took speed scaling overhead into account and offers a system-wide view by considering not only the CPU, but also bus and memory. The speed scaling overhead is automatically accounted within the CPU budget assigned to each task. In addition, the authors proposed to manage also the static slack which, otherwise, would be entirely allocated to non real-time tasks. Their proposal consists of increasing the utilization values of real-time tasks to exploit the entire remaining static slack, even though, the actual execution times are not changed. In such a way, at runtime, the overestimated utilization is automatically transformed into dynamic slack which is, in turn, easily handled within the presented framework.

#### Dynamic and static slack reclaiming

All the algorithms reported here consider periodic tasks whose computational times scale linearly with the speed (C(s) = C/s). Moreover, the speed scaling overhead is

considered negligible and the power consumption is modeled as  $P(s) = \beta \cdot s^3$ .

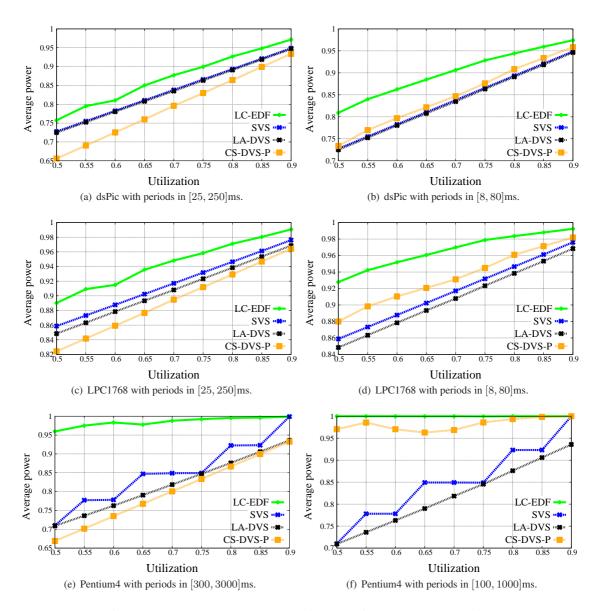

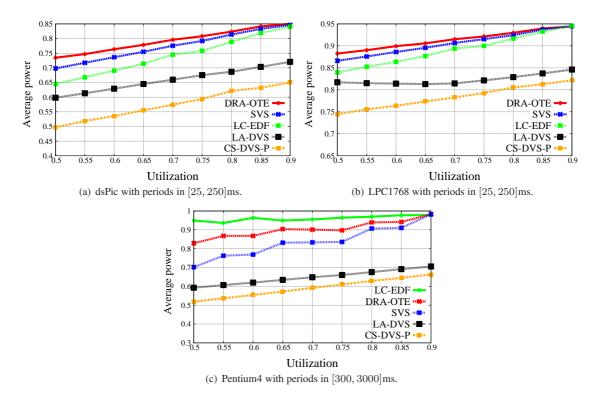

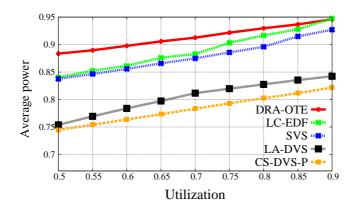

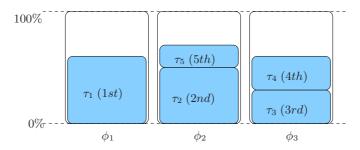

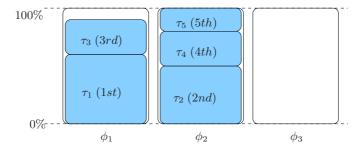

Pillai and Shin [PS01] proposed three algorithms considering both EDF and RM scheduling policies. The first approach, referred to as Static Voltage Scaling (SVS), runs offline and exploits only the static slack: when the system starts, the running speed is set equal to the lowest available speed level which guarantees the task set feasibility. Then, the cycle-conserving algorithm (cc-EDF and cc-RM) is introduced. The algorithm, at every scheduling event, sets the running speed to the lowest level that guarantees timing constraints using the actual execution time for the completed jobs and the WCET information for future jobs. Notice that the cc-EDF algorithm generates a schedule identical to the SVS schedule if the actual workload is identical to the worst-case. The last proposed algorithm, called Look-Ahead RT-DVS (LA-DVS), runs only under EDF and aims at further reducing the running speed of the current (earliest-deadline) job as much as possible, while still guaranteeing the deadlines of other jobs. Hence, although the actual speed until the next deadline can be quite low, it may be necessary to execute future jobs at high speed levels to meet their timing constraints, in case the current job takes (close to) its WCET. However, this side effect is significantly reduced thanks to frequent early task completions in practice.

Aydin et al. [AMMMA04] proposed three algorithms at increasing complexity and sophistication levels, for periodic real-time tasks. All the algorithms assume a continuous speed range and a negligible switching overhead. The first algorithm computes the running speed as the utilization of the task set (similar to SVS) and it is not changed at runtime. The algorithm works with all the scheduling algorithms which guarantee the full utilization of the processor while guaranteeing the feasibility, such as EDF and Least Laxity First (LLF). The second algorithm (Dynamic Reclaiming Algorithm, DRA) uses a queue structure called  $\alpha$ -queue where each element contains the deadline and the remaining execution time  $rem_i$  of task  $\tau_i$ . When a task arrives, its absolute deadline and execution time at the optimal speed are inserted in the  $\alpha$ -queue. At every scheduling event, the  $rem_i$  field of the  $\alpha$ -queue's head is decreased by the amount of the elapsed time since the last event. In other words, the  $\alpha$ -queue represents the ready queue in the worst-case schedule at that specific time. Once a new job is about to be scheduled, its remaining execution time is summed with the  $rem_i$  values in  $\alpha$ queue whose deadlines are less than or equal to the task in question, and then the speed is scaled accordingly. This procedure enables the current job to reclaim the dynamic slack of already completed higher-priority jobs, while still ensuring it does not complete later than the instant when it would complete in the worst-case schedule. The algorithm is improved by incorporating the One Task Extension (DRA-OTE) technique which, when there is only one task in ready queue and its worst-case completion time at the current speed falls earlier than next scheduling event, slows the speed down to let the task terminate at the next event. The third algorithm, Aggressive Speed Reduction - AGR 1, relies on the idea that when all the ready tasks have deadlines earlier than the next task arrival time, then the computational budget can be exchanged among those tasks without affecting the feasibility. Specifically, in such a situation the algorithm reduces the speed of the current job by allocating some of the CPU time of other lowpriority ready tasks. This approach may force other pending tasks to execute at very high speed levels to meet their deadlines in some execution scenarios. To mitigate this, another algorithm (AGR-2) is proposed, which limits the extent of the slowdown for the current task by considering the information about the average case workload.

#### 3.1.2 DPM algorithms

DPM-based energy management algorithms are based on the principle of putting the processor to low-power (sleep) states at runtime. A main problem involved in DPM research is to make sure that the transitions are beneficial in terms of energy savings, because as explained in Section 2.1, there is a minimum time interval (called the *break-even time*) that amortizes the time and energy overhead associated with each transition. In fact, a common technique is to use the *task procrastination* technique which postpones the execution of the ready jobs as much as possible by exploiting the system slack at that time, thereby compacting busy periods and yielding long idle intervals. By doing so, the number of runtime transitions and overhead are also reduced. On the other hand, utmost care must be taken to avoid the violation of the timing constraints in real-time systems, when employing the procrastination technique.

The rest of this section introduces the most interesting offline and online DPM approaches proposed in the literature

All the algorithms discussed in this section consider the break-even times for the CPU explicitly in their analysis. Although some papers consider only a single low-power state, we note that their approach can be easily extended to systems with multiple low-power states by exploiting the "deepest" inactive state with break-even time shorter than or equal to the length of the available idle interval.

#### Offline DPM algorithms

Rowe et al. [RLZR10] presented two techniques to harmonize task periods with the aim of clustering task executions (i.e., to combine processor idle times whenever possible). The framework assumes a system without the DVFS feature. The first algorithm, Rate-Harmonized Scheduler (RHS), introduces the concept of harmonizing period  $(T_H)$ . The scheduler is notified by the task arrivals only at the integer multiples of the harmonizing period. The harmonized period is computed as a function of the shortest period. For instance, if the effective arrival time is at 3.5 and the harmonizing period is 1, then the scheduler considers this arrival only at time 4. Since all the arrivals are considered at integer multiples of the harmonizing period, if there is no task to execute, then the processor can be put in sleep state until the next period. The approach considered fixedpriority tasks whose priorities are assigned by the Rate Monotonic policy. Although the exact schedulability can be checked by evaluating the worst-case response time through the Time Demand Analysis, the utilization bound for schedulability reduces to 0.5, in the general case. The second algorithm, called *Energy-Saving RHS (ES-RHS)*, introduces a new task with period equal to  $T_H$  (highest priority). Its computation time is evaluated by considering  $T_H$  and the spare utilization. The new task enables putting the processor to sleep state when it is invoked and when its computational budget is longer than or equal to the break-even time. The main advantage of ES-RHS with respect to RHS is that the idle times generated by task early terminations extend the sleep interval in the next period. In such a way, multiple short idle intervals are combined to a single longer interval, giving an advantage over RHS. Two low-power states are taken into account, idle and sleep, considering a short and long break-even time, respectively. In addition, a real implementation on a sensor node is reported.

#### Online DPM algorithms

Lee et al. [LRK03] proposed two leakage control algorithms for procrastinating task executions as long as possible, to prolong and compact idle intervals, both under dy-

namic (LC-EDF) and fixed (LC-DP) priority scheduling. Both algorithms assume periodic tasks with periods equal to the deadlines and a system without DVFS feature. The main idea behind the algorithms is to compute at each job arrival the maximum time the job can be delayed without missing its deadline. Under EDF scheduling, whenever the CPU becomes idle, LC-EDF computes the maximum time duration  $\Delta_k$  that the task with the earliest arrival time ( $\tau_k$ ) can be delayed by using the following equation:

$$\sum_{i\in\{1,...,n\}/\{k\}}\frac{C_i}{T_i}+\frac{C_k+\Delta_k}{T_k}=1.$$

Then, the system is put to the low-power state (procrastinated) for  $\Delta_k$  time units. If another higher-priority task  $\tau_j$  with absolute deadline shorter than the  $\tau_k$ 's deadline arrives before the end of the procrastination interval, the procedure is executed again, by considering the length of the idle interval already elapsed,  $\delta_k$ , and obtaining the new value of the procrastination interval  $\Delta_j$  through the following equation:

$$\sum_{i\in\{1,\dots,n\}/\{k,j\}}\frac{C_i}{T_i}+\frac{C_k+\delta_k}{T_k}+\frac{C_j+\Delta_j}{T_j}=1.$$

For fixed-priority systems, the authors resort to the *dual priority* scheme [DW95] in order to to compute the length of the procrastination interval. More precisely, the additional sleep time is computed as the minimum *promotion time*  $Y_i$  (relative deadline minus the worst-case response time) among the tasks in the lower run-queue. The promotion time of each task is computed statically as the difference between its relative deadline and the worst-case response time, derived from Time Demand Analysis. The main limitation of such an approach is that it requires a dedicated hardware to implement the algorithms and manage sleep and wake up operations. Although task early terminations are not directly involved in the analysis, the work-conserving (non-idling) nature of the algorithms can indirectly incorporate the dynamic slack at run-time.

Awan and Petters [AP11] proposed an algorithm under EDF, called *Enhanced Race-To-Halt* (*ERTH*), which targets at dynamically monitoring and accumulating both static and dynamic slack, in order to apply the DPM technique effectively. The authors considered sporadic tasks with different criticality (hard, soft real-time and best effort) and a processor model with several low-power states. Essentially, the algorithm uses a single counter to keep track of both static and dynamic slack. When the system is idle, the processor is put to the deepest low-power state with break-even time not exceeding the amount of the existing slack at that time. Similarly, if there are some ready tasks, and the amount of available slack is longer than or equal to the break-even time, then the processor is switched off as long as possible without causing any deadline miss. On the other hand, if the amount of slack is less than the break-even times, the processor executes the current workload at the maximum speed and then attempts to switch to a sleep state when idle. The proposed algorithm has been compared with LC-EDF, showing that, under certain conditions, it achieves a lower energy consumption.

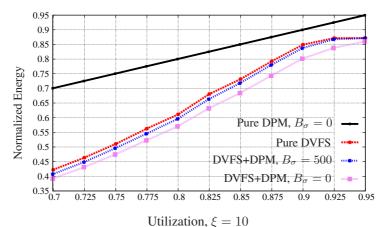

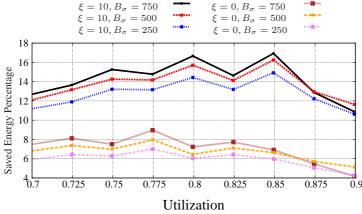

#### 3.1.3 Integrated DVFS-DPM algorithms

This section considers the algorithms that use both DVFS and DPM techniques. Specifically, these *integrated* algorithms exploit both speed scaling and low-power states to maximize energy savings, unlike the techniques that use only one feature.

First, the algorithms that make the speed scaling decisions offline are considered then, those that compute the speed scaling factors online are introduced.

#### Offline speed scaling

All the algorithms reported here are designed for periodic real-time tasks and do not explicitly consider dynamic slack.

Jejurikar et al. [JPG04] proposed an approach (CS-DVS-P) based on the critical speed analysis and task procrastination, for periodic preemptive tasks executed under the EDF scheduling policy. Offline, the algorithm first computes the lowest speed (higher than or equal to the critical speed,  $s^*$ ) that guarantees the task set feasibility. Then, the maximum amount of time ( $Z_i$ ) each job of task  $\tau_i$  can spend in the sleep state within its period without leading to any deadline miss is evaluated using the following equation:

$$\frac{Z_i}{T_i} + \sum_{k=1}^i \frac{C_k}{T_k} = 1.$$

At runtime, when there is no pending job, the processor is put in a low-power sleep state (as deep as justified by the break-even time and available slack) until the next job arrival. When a job arrives and the processor is still in sleep mode, an external controller continues to keep the processor in sleep state for an additional time period computed as the minimum of remaining time to wake-up and the precomputed delay of the newly arriving job.

[JG04] extended the algorithm to fixed-priority (CS-DVS-P1) and dual-priority (CS-DVS-P2) systems. With respect to the original algorithm given in [JPG04], only the computation of the  $Z_i$  values is different, leaving the online step the same. Moreover, the authors showed that the dual-priority scheduler is able to guarantee longer  $Z_i$  values than the fixed-priority scheduler.

Chen and Kuo [CK06] showed that the DPM part of the algorithm proposed by [JG04] may lead to deadline misses, thus they proposed two solutions to avoid them, Online Simulated Scheduling (OSS) and Virtual OSS (VOSS). Both algorithms consider periodic independent tasks for fixed-priority systems where priorities are assigned according to the Rate Monotonic policy. Initially, all tasks are assigned the lowest speed that still guarantees the feasibility, subject to the lower bound of critical speed. OSS runs when the ready queue is empty and simulates the execution of tasks that arrive earlier than the earliest absolute deadline, accounting for their idle time. Then, the arrivals of those tasks are delayed for the relative accounted time, while the processor is put in sleep mode until the first job arrival (if and only if the available idle time is longer than the break-even time). VOSS enhances OSS by combining the online simulation with the virtual blocking time. Specifically, in the simulation phase, the algorithm considers as arrival time the value of  $r_{i,k} + Z_i$  where  $Z_i$  represents the maximum blocking tolerance that each task can afford without causing deadline misses.  $Z_i$  is computed offline through the response time analysis. In this way, the arrivals of the tasks taken into account result further delays than those provided in OSS, leading to longer sleep intervals. The complexity of the online step is due to the simulation phase, which is  $O(n \cdot \log(n))$ , while the offline computation of the virtual blocks has pseudo-polynomial complexity.

#### Online speed scaling

Jejurikar and Gupta [JG05a] extended the algorithm in [JPG04] to explicitly consider task early terminations on dynamic priority systems. The algorithm is called *Dynamic Slack Reclamation with Dynamic Procrastination (DSR-DP)*. The first improvement

consists in collecting unused computation times (dynamic slack) in a *Free Run Time* (*FRT*) list, which also includes information of the priority of the task that generated it. To prevent any deadline miss, each job can only use the dynamic slack generated by tasks with higher or equal priority. Such additional CPU time is partially exploited to slow down the processor speed while the job is executing and also to extend the time spent in sleep state. Specifically, the slack distribution algorithm primarily uses the additional slack to scale the speed down and, if the critical speed is reached, the residual time is used to extend the sleep interval.

Irani et al. [ISG07] introduced two techniques for dynamic speed scaling with and without low power states: DSS-S and DSS-NS. DSS-NS is based on using mostly speed scaling while DSS-S executes the workload at the maximum speed to maximize the use of the low-power states. Both the P(s) and P(s)/s functions are assumed to be convex and the scheduler implements the EDF policy. An offline algorithm for DSS-S and two online solutions for DSS-S and DSS-NS were presented. The main idea behind the offline algorithm is to procrastinate tasks and execute them at a speed no lower than the critical speed. Under the assumptions of convexity, the proposed offline algorithm achieves an approximation ratio of 3 with respect to the optimal solution. However, the overheads due to the speed scaling and state transition are not taken into account.

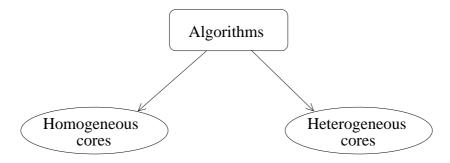

#### 3.2 Energy-aware scheduling on multi-core systems

This sections presents the state-of-the-art algorithms for multi-core platforms, exploiting the taxonomy shown in Figure 3.2. Algorithms are broadly divided according to the heterogeneity of the system they assume to deal with. More precisely, the first kind of algorithms assumes to handle a set of homogeneous cores whose performance and consumptions are identical, whereas the second group takes into account heterogeneous cores (with at least two different kinds of cores). Such algorithms are detailed in Section 3.2.1 and Section 3.2.2, respectively.

For each class, algorithms are further collected according to the approach they implement: partitioned, global or hybrid. The first one statically assigns a task to a specific core, forbidding its jobs to migrate onto another core even though it is idle. This method allows designers to easily check the system feasibility but, in many cases, it leads to a waste of computational resources. Global approaches improve the system utilization by allowing task migration at any time in any processor, but are more difficult to analyze and may introduce significant run-time overhead. Hybrid scheduling approaches try to combine the two previous strategies to reduce their drawbacks and exploit their advantages.

#### 3.2.1 Homogeneous cores

One of the first papers which has considered the partitioning problem of a set of periodic tasks on a multi-core system was proposed by Aydin and Yang [AY03]. The authors compared the behavior of four well-known heuristics (First-Fit, Next-Fit, Best-Fit and Worst-Fit) on a system whose dissipation is highly dependent on the running speed. The work stated that Worst-Fit Decreasing (WFD), which aims at balancing the workload among the cores, is the most effective for reducing the energy consumption while considering cubic power functions. More precisely, spreading the workload among all the cores lets us use many processors which run at a low frequencies. On the other hand, collecting the workload on few cores (and switching off the others) is not

Figure 3.2: Algorithm taxonomy for multi-core systems.

an effective strategy as the energy dissipation of those few cores is much higher than having all cores active and running at low speeds.

Yang et al. [YCK05] proposed an algorithm which partitions a set of frame-based tasks (with same period and deadline) using the Worst-First strategy and then scales speed in particular instant according to the task features. In addition, all cores must share the same running frequency and voltage, meaning that the speed selection is done according to the most loaded CPU. However, cores are allowed to enter into a low-power state independently. Although the algorithm is characterized by a good approximation factor with respect to the optimal scheduling, the authors made several non-realistic assumptions, such as continuous and infinitive frequency range ( $s \in [0, \infty]$ ) and negligible consumption in idle state.

Kandhalu et al. [KKLR11] considered the issue of partitioning a set of periodic real-time tasks on multi-core systems characterized by a single voltage island (all the processors share the same voltage and frequency). Moreover, deadlines are assumed to be equal to periods. Within a voltage island, the core with the highest load is the one which imposes the running frequency. In other words, the load balancing is crucial. Since it has been already proven that, under EDF, the overall energy dissipation is minimized when the load is perfectly balanced among the cores, the authors focused their attention on tasks with fixed priorities. They proved the approximation upper bound for the classical Worst-First Decreasing heuristic and then, their own algorithm (Frequency Assignment Algorithm - SFAA) was provided to overcome several limitation of the state of the art by taking explicitly task periods into account during the partitioning. Finally, the power model was obtained from a NVIDIA's Tegra 2 processor.

Ghasemazar et al. [GPP10] provided a global approach based on the control analysis to minimize the overall energy consumption while guaranteeing the desired throughput. The homogeneous cores, which share the L2 cache, are assumed to be switched off independently. When a new job arrives, the hierarchical scheduler computes the number of core to keep active and then a feedback control loop sets the frequency which lets the system provide the required throughput. Finally, the new job is assigned to a core which is in charge of executing it according to its priority.

Pagani and Chen [SJJ13] carried out an analysis that, independently from the task partitioning algorithm, found the approximation ratio of the Single Frequency Approximation (SFA) scheme on multicore voltage islands with respect to the optimal solution. More precisely, SFA consists of setting the frequency of the voltage island equal to the maximum utilization among the cores. Despite its simplicity, SFA is the easiest algorithm to be implemented and it is widely used in actual systems.

Unlike other papers, Langen and Juurlink [dLJ06] considered a multi-core proces-

sor whose cores can vary their frequency independently. The authors considered a scenario in which the leakage power consumption is as important as the dynamic dissipation and then, they integrated such a contribution into the analysis. More precisely, according to the actual value of the leakage current, the provided algorithm (referred to as LAMPS) computes the number of core to be kept active, their frequencies and voltages in order to minimize the energy dissipation. Results were obtained by comparing the energy consumption with the Schedule and Stretch (S&S) algorithm which aims at spreading as much as possible the workload among the available cores (similarly to what WFD does).

Recently, Carrol and Heiser [CH14] have revisited several common beliefs, showing empirically that on the latest-generation ARM multi-core processors, the static power is almost negligible. First, they extended the concept of critical speed to each core, in order to define the frequency which locally optimizes the energy consumption. Then, a governor for the Linux *cpufreq deamon* was implemented whose algorithm executes the following steps every 100ms:

- computing the slowest frequency which guarantees the feasibility on each core;

- if such a speed is higher than the critical one, then wake an asleep core up;

- if such a speed is lower than the critical one, then put a core in sleep state.

#### 3.2.2 Heterogeneous cores

Petrucci et al. [PLM<sup>+</sup>12] considered the problem of partitioning a set of independent tasks on heterogeneous systems. Such systems are composed of a set of high performance sophisticated cores and a set of low-power cores. Their analysis relies on the fact that CPU-intensive applications should run on performing cores, while I/O applications should take advantage of low-power cores. More precisely, they introduced a periodic partitioning algorithm (implemented as ILP problem) which migrates tasks among cores according to their actual phase (interval in which the code is mostly either CPU or I/O intensive) in order to better exploit the energy efficiency of each core.

Awan and Petters [AP13] proposed a two-step partitioning algorithm for heterogeneous systems with two kind of cores. Firstly, the algorithm assigns tasks to the core which optimizes its execution while considering only the dynamic energy consumption. Then, the second step reduces the static energy consumption by improving the effective use of low-power states, involving tasks' parameters into the analysis (such as periods and execution times). For example, allocating a task with short period (despite its execution time) may prevent the system to put the core in a deep low-power state even though the overall utilization is low. For such a reason, tasks which forbid the use of deep sleep states should be moved somewhere else in order to reduce the static energy consumption.

Schranzhofer et al. [SCT10] proposed two different partitioning approaches for the problem in question. The first one assigns tasks to cores statically, independently from the actual context, in a static fashion. The second solution assigns a task to a core according to the actual scenario at runtime. More precisely, the mapping is chosen among several possible alternatives which have been pre-computed at design time. Although the first approach is less flexible than the second, it requires a smaller amount of memory to store the additional information (in the form of a mapping table).

Hung et al. [HCK06] addressed the energy-efficient real-time scheduling issue on systems mounting two cores with and without speed scaling feature, respectively. The

workload consists of a set of periodic real-time tasks and jobs which may migrate from one core to the other when necessary. When the power consumption of the non-DVFS cores is independent from the workload, a fully polynomial-time approximation scheme (FPTAS) is provided for energy-efficient scheduling. On the other hand, when the energy consumption of the non-DVFS cores depends on the assigned workload, a 0.5-approximation algorithm is introduced to save energy.

#### 3.3 Similar problems

This section briefly overviews other problems related to the energy issue which consider additional objectives. Since the energy harvesting problem has been addressed in this thesis, a deeper analysis is provided for it in Section 3.3.1.

An interesting problem is related to the joint scheduling of real-time and non real-time tasks, where the goal is to minimize the overall energy consumption, while guaranteeing real-time constraints and reducing the response time of non real-time tasks. As in the case of real-time tasks, providing short response time to the non real-time tasks, in general, conflicts with the energy saving objective. Aydin and Yang [AY04] investigated the impact of speed scaling decisions on the responsiveness of non real-time tasks and overall energy consumption, while still meeting the timing constraints of hard real-time tasks. Saewong and Rajkumar [SR08] proposed to exploit the slack available in real-time tasks to execute non real-time tasks at the maximum speed to minimize their response time.

The energy-aware scheduling of tasks that share resources which must be accessed in non-preemptive fashion is another important problem that was addressed in [ZC04, LKL07, JG05b]. In [ZAZ12], the energy-aware scheduling of periodic real-time tasks with task-level reliability constraints has been considered.

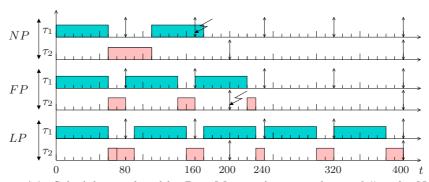

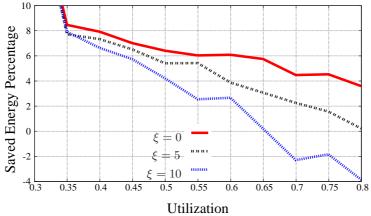

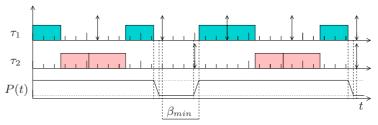

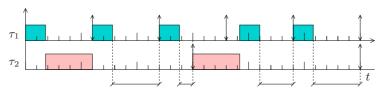

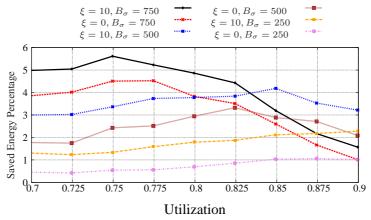

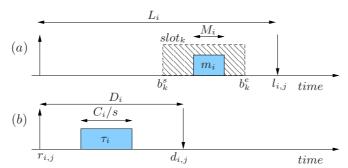

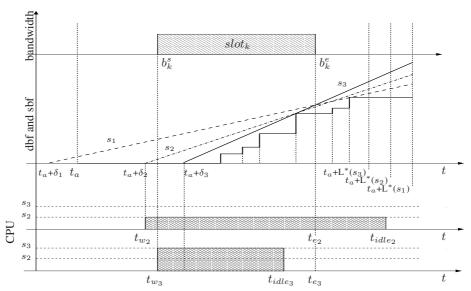

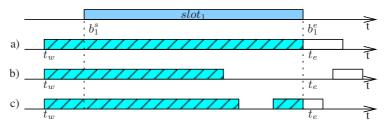

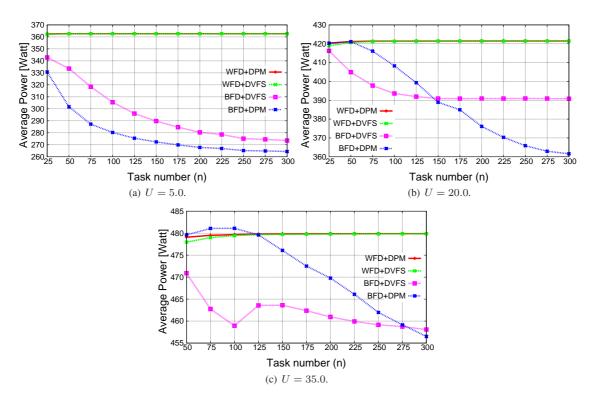

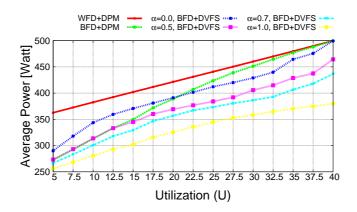

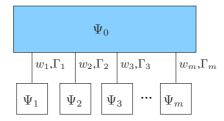

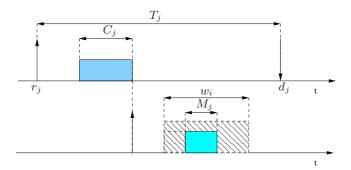

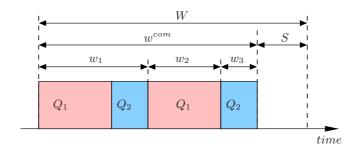

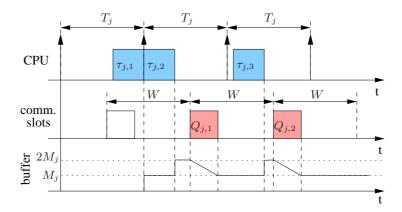

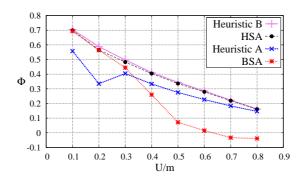

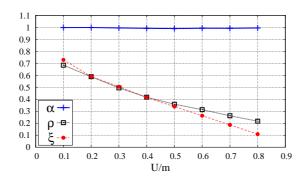

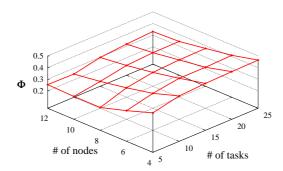

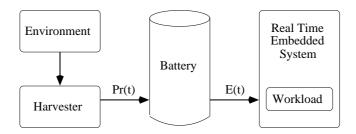

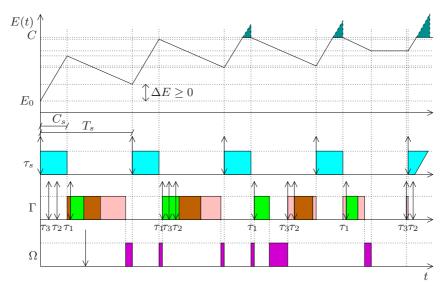

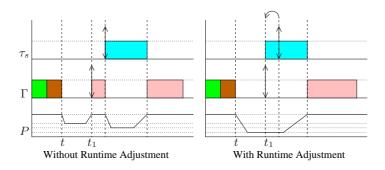

A more general energy-aware co-scheduling problem includes both the CPU and devices in the analysis. Devices are typically considered speed independent, providing low-power states and requiring non-preemptive access [CG06, DA08, YCK07]. Other authors considered the problem of co-scheduling tasks and messages [YPH<sup>+</sup>09].