Matteo Morelli

A System-Level Framework for the Design of Complex Cyber-Physical Systems from Synchronous-Reactive Models

Anno Accademico 2014-2015

Corso di perfezionamento in Tecnologie Innovative

# A System-Level Framework for the Design of Complex Cyber-Physical Systems from Synchronous-Reactive Models

Autore Matteo Morelli Tutor Prof. Marco Di Natale

## Abstract

THE goal of this research is the definition of a design process, supported by tools, for the development, verification and deployment of time-sensitive cyber-physical systems (CPS) control applications. Safe interaction between a robotic arm and a human co-worker, robotic-assisted surgery, flight control of an aerial robot; but also, data acquisition and coordination of smart traffic light systems, advanced driver assistance systems in cars and operation of smart grids in public infrastructures — all of these are examples of time-sensitive CPS control applications. They are realized as software algorithms (control software) whose correct functioning depends not only upon the logical correctness of control actions, but also upon the time in which these actions are performed.

Control software is in turn realized as a set of software tasks exchanging messages on top of networks of embedded computers running real-time operating systems (execution platform). The realization of control software is difficult, because a number of factors may affect the final performances, such as, how control functions are mapped into tasks, how tasks are deployed onto the computing nodes, the types of resources for local communication, networks and protocols for communication among remote nodes. And it is made even more challenging by the need to keep the software development costs low and the time-to-market short, that mandates careful selection and efficient usage of hardware/software resources.

As of today, embedded control application design is carried out in stages. In the first stage, a Model-Based Design approach is used, where models of control functionality are designed and verified by simulation in a virtual environment. In most cases functional models are based on a Synchronous-Reactive (SR) execution paradigm. All the computations and communications are assumed to complete within the interval between two events in logical time and implementation aspects (including the time delays introduced by the execution platform) are not considered. In the next stage, a task implementation (code) that realizes the control law is produced. Then, the software code is analyzed onto prototypical (or even the final target) hardware to verify that timing constraints are satisfied. This approach impedes design-space exploration, and defers the validation of the selected implementation (hardware/software) until late, in the integration/testing stage.

In this work, we propose a Model-Driven Design process and tools, encompassing the tight integration of control, hardware and real-time software architectures from the very beginning, at model level. This framework supports the transition from the functional model to the code implementation (with the preservation of the original model semantics), and enables designers to explore tradeoffs between delays (of task scheduling and messages) and control performances

#### ABSTRACT

when a semantics-preserving implementation of functionality is not achievable. The framework is based on *standards* (Simulink and OMG's SysML/MARTE, MOFM2T and M2M) and *open* (EMF-based) tools (Papyrus, Acceleo and QVTo).

We define a common semantic domain and rules for the integration of SR models of control with models representing the execution platform and the software tasks and messages that realize the functions. Models incorporate and expose appropriate information to allow accurate prediction of control performance and timing properties of a candidate software implementation. The design cycle is a sequence of tool-assisted stepwise refinements which is iterated until the implementation satisfies the initial specification. Models and rules are defined to generate semantics-preserving deployment of control functionality on top of the real-time capable, component-based middleware Orocos-RTT that is very popular among robotics practitioners (researchers and industry).

When the full preservation of functional model semantics cannot be guaranteed by the implementation, designers may resort to simulation to gather important information about the estimated impact of time delays (dependent on code execution, scheduling of tasks, and network communication latencies) on the control performances. System-level prediction of timing behavior is enabled by T-Res, a Simulink-based co-simulation framework which integrates external simulation engines for real-time scheduling and network communication. The advantages of this approach are demonstrated onto a model of a simulated rotorcraft Unmanned Aerial Vehicle (UAV).

Finally, we define a simulation-driven optimization process for the automated synthesis of software architecture configurations on single-core platforms, in those situations where there are no feasible task-sets for the deadlines determined in the control design stage. The approach couples MILP-based optimization with simulation and extend the traditional design flows to include the exploration of relaxed deadlines and order-of-execution constraints. The experiments conducted on a simulated UAV case study show the benefits of the approach.

To Annalisa and Leandro.

## Acknowledgements

THIS work would not have been possible without the advice and support of many. Firstly, I want to thank my advisor, Marco Di Natale, for having helped me to get into the domain of Model-Driven Design and for having always been available to answer my often confusing questions and discuss concepts in detail. Marco, I greatly appreciated your style, your constructive criticism and the freedom you gave me to work independently.

I want also to thank Giuseppe Lipari for having actively supported the work on RTSim and Simulink, and for the interesting discussions on design patterns in Object-Oriented Programming, which have profoundly influenced the way I now develop software. Many thanks go also to Mauro Marinoni for his endless patience and for having always provided immediate support with hardware issues and related discussions. Thanks to Enrico Bini and Giorgio Buttazzo, who, though less directly involved in my research, have repeatedly provided valuable suggestions and feedback.

A Special thank goes to Fabio Cremona, who worked with me to develop T-Res. Fabio, I appreciated your pragmatism and determination to deliver a working system. Thank you for the enjoyable hours of fighting to embed the OMNeT++ simulation kernel into Simulink. It has been a pleasure to work with you.

I want to thank my colleagues of LISE Lab. at CEA-List Yasmina Seddik, Sara Tucci-Piergiovanni and Chokri Mraidha, who have co-authored the work on the automated synthesis of real-time control tasks. Thanks Sara and Yasmina for the friendly welcome in Paris and also for the practical help at the beginning of my stay in France.

I wish to thank Federico Moro, Luigi Palopoli, Tizar Rizano and Daniele Fontanelli, of DISI Lab. at the University of Trento for having shared (and explained) their Simulink models and C++ code for the (ongoing) project on the robotic car testbench.

I am very grateful to Paolo Gai who shared his experience as a former PhD student of ReTiS Lab. and pointed me in the right direction at the end of my Master's Degree program. And thanks also to Simone Mannori and Roberto Bucher, who first introduced me into the world of code-generation, since the days of the Scicos-RTAI Code Generator and the Robotics Toolbox for Scilab/Scicos.

Thanks to Alessandro Passaro, for the helpful discussions on Acceleo at the beginning of my PhD work, and to Dario Di Stefano and Riccardo Schiavi (Evidence Srl.), for their support with E4Coder. In general, thanks to all the friendly and smart guys at Evidence Srl. (Errico, Davide, and many others).

#### ACKNOWLEDGEMENTS

Thanks to all the people of ReTiS Lab., who were next to me in this long project and adventure: Andrea and Riccardo (who enrolled in the PhD Program with me in November 2011); the former PhD students Christian, Matteo, Claudio, Giulio, Francesco, Juri, Mario, Stefano, Marco and Daniele; the current PhD students Youcheng, Paquale, Carmelo, Alessandra, Alessandro, Andrea, David, Davide, Simone and Luca; the research fellows Anna Lina, Gabriele, Gianluca, Daniel, Paolo, Mariano; and all the people of the staff Igor, Claudio, Valentina, Annalisa, Stefania, Sabrina, Elena, Antonio, Francesca, Valeria, Ketty and Isabella.

Last, but not least, I desire to thank my family. My parents, Paolo and Paola, who have been encouraging throughout my entire lifetime, and for all their help. Flavio and Rosanna, for coming to Pisa so many times to help Annalisa when I was traveling.

Annalisa and Leandro, this work is dedicated to you. Grazie Annalisa per essere sempre dalla mia parte e per il tuo incessante supporto. Grazie per la determinazione con cui lavori e ti prendi ogni giorno cura della nostra famiglia (inclusi ovviamente Spike, Jackie, Sansone, Elvis e Priscilla—grazie anche a voi!), adesso che io sono lontano. Il tuo esempio mi spinge ogni giorno a dare il massimo. Sei una moglie e una madre meravigliosa. Leandro, grazie per prenderti cura della mamma e per i tuoi incoraggiamenti. Ho stretto i denti come mi hai detto di fare tante volte e... Visto? Ce l'abbiamo fatta! Ti voglio bene, piccolo mio  $\heartsuit$

## Contents

| Abstract                                                                        | iii  |

|---------------------------------------------------------------------------------|------|

| Acknowledgements                                                                | vii  |

| List of Figures                                                                 | xiii |

| List of Tables                                                                  | xvii |

| Chapter 1. Introduction                                                         | 1    |

| 1.1. Cyber-Physical Systems (CPS)                                               | 1    |

| 1.2. Current Design Workflows                                                   | 2    |

| 1.3. Platform-Based Design (PBD)                                                | 3    |

| 1.4. Research Objectives                                                        | 5    |

| RI.1. Models and abstractions for the verification of implementation properties | 6    |

| RI.2. Semantics-preserving application deployments                              | 7    |

| RI.3. Simulation tools to predict the system-level timing behavior              | 7    |

| RI.4. Automatic software architecture configuration                             | 7    |

| 1.5. Thesis Outline                                                             | 8    |

| Chapter 2. Methods and Tools for System-Level Modeling and Design               | 9    |

| 2.1. Introduction                                                               | 9    |

| 2.2. Model-Based Design (MBD)                                                   | 9    |

| 2.3. Model-Driven Engineering (MDE)                                             | 10   |

| 2.4. Frameworks for Heterogeneous-Model Integration                             | 11   |

| 2.5. System-Level Approaches in Automotive and Robotics                         | 11   |

| 2.6. Simulation of Platform's Delay Effects                                     | 13   |

| 2.7. Discussion and Conclusions                                                 | 15   |

| Chapter 3. Design-Process Flow and Platform Meta-Models                         | 17   |

| 3.1. Introduction                                                               | 17   |

| 3.2. Process Flow Based on Standard Technologies                                | 20   |

| 3.3. Functional Modeling                                                        | 21   |

| 3.3.1. Functional Modeling in Simulink and EMF                                  | 21   |

| 3.3.2. M2M Transformation to SysML                                              | 22   |

| 3.4. Platform Modeling                                                          | 26   |

| 3.4.1. Physical Platform Modeling                                               | 26   |

| CONT  | ENTS |

|-------|------|

| 00111 |      |

| 3.4.2. BSW Resources Modeling                                                     | 28 |

|-----------------------------------------------------------------------------------|----|

| 3.5. Software Architecture Modeling                                               | 30 |

| 3.6. Summary                                                                      | 32 |

| Chapter 4. Generation of Semantics-Preserving Robot Controls from Simulink Models | 35 |

| 4.1. Context and Positioning                                                      | 35 |

| 4.2. Constraints in the Implementation of Synchronous (Simulink) Models           | 37 |

| 4.2.1. Model Assumptions and Basic Formalization of the Synchronous Semantics     | 37 |

| 4.2.2. Software Implementation and Preservation of Data-Flows                     | 38 |

| 4.3. The Orocos-RTT Run-Time Environment                                          | 39 |

| 4.4. The Code-Generation Process                                                  | 40 |

| 4.4.1. Generation of Task Synchronization Infrastructure                          | 41 |

| 4.4.2. Generation of Task Code                                                    | 45 |

| 4.4.3. Implementation of the Functional Communication Links                       | 45 |

| 4.5. Summary                                                                      | 46 |

| Chapter 5. Platform-Aware Control Simulations in Simulink Through Co-Simulation   | 49 |

| 5.1. Context and Positioning                                                      | 49 |

| 5.2. How the Simulink Engine Simulates a Dynamic System                           | 51 |

| 5.3. Platform Simulators and Execution Models                                     | 52 |

| 5.3.1. Discrete-Event Platform Simulators                                         | 52 |

| 5.3.2. Execution Model of Real-Time Tasks                                         | 52 |

| 5.3.3. Execution Model of Network Communication                                   | 54 |

| 5.4. The T-Res Co-Simulation Environment                                          | 56 |

| 5.4.1. Architecture                                                               | 56 |

| 5.4.2. Simulink Implementation of Platform Execution Models                       | 57 |

| 5.4.3. Interface to Other Platform Simulators                                     | 62 |

| 5.5. Application Examples                                                         | 65 |

| 5.5.1. PID Control of Three Networked DC-servo Systems                            | 65 |

| 5.5.2. Scheduling-Aware Design of Attitude Control for a Simulated Quadrotor      | 67 |

| 5.6. Integration in the Proposed System-Level Design Flow                         | 71 |

| 5.7. Summary                                                                      | 75 |

| Chapter 6. Simulation-Driven Process for Automated Software Synthesis             | 77 |

| 6.1. Context and Positioning                                                      | 77 |

| 6.2. System Model                                                                 | 79 |

| 6.2.1. Definition of Mapping                                                      | 79 |

| 6.2.2. Response-Time Analysis                                                     | 79 |

| 6.3. Optimization Model                                                           | 80 |

| 6.3.1. Optimization Variables                                                     | 80 |

| 6.3.2. Constraints                                                                | 81 |

| 6.3.3. Optimization Metrics                                                       | 83 |

x

| CONTENTS                                              | xi  |

|-------------------------------------------------------|-----|

| 6.4. Simulation                                       | 84  |

| 6.5. Application Example                              | 84  |

| 6.5.1. Case Study Definition                          | 84  |

| 6.5.2. Computation of Deadline Approximations         | 84  |

| 6.5.3. Exploration Strategies and Application of MILP | 86  |

| 6.5.4. Evaluation of Candidate Designs                | 87  |

| 6.6. Summary                                          | 90  |

| Chapter 7. Conclusions                                | 93  |

| 7.1. Contributions                                    | 93  |

| 7.2. Limitations (Ongoing Work)                       | 95  |

| 7.3. Opportunities for Future Research                | 97  |

| List of Publications                                  | 99  |

| Bibliography                                          | 101 |

## List of Figures

| 1.1  | CPS: typical realization and real-time guarantees of control software stack.                                            | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The PBD concept (reproduced from [ <b>DNSV10</b> ]).                                                                    | 4  |

| 1.3  | The levels of platform abstractions that are of concern in this thesis.                                                 | 6  |

| 3.1  | Platform models, mapping process and application scenarios for the proposed design flow.                                | 17 |

| 3.2  | Examples of safety-critical and performance-sensitive systems in automotive.                                            | 18 |

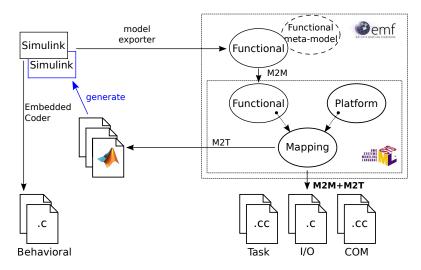

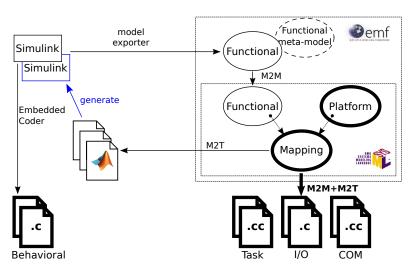

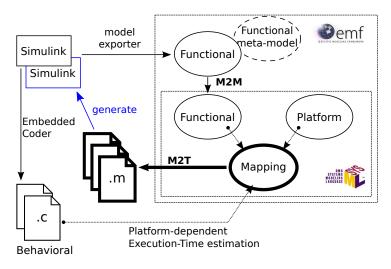

| 3.3  | Heterogeneous model integration and code generation by the framework tools.                                             | 21 |

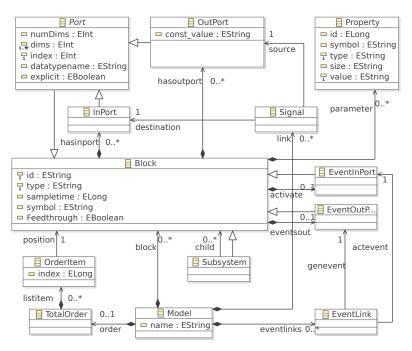

| 3.4  | The Ecore meta-model for the functional part.                                                                           | 22 |

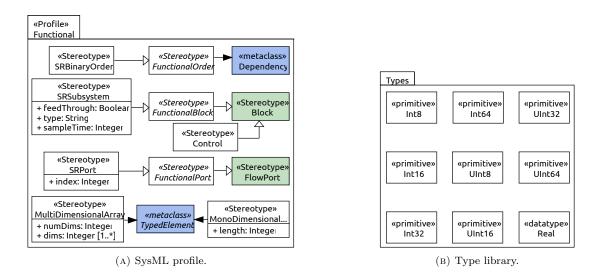

| 3.5  | The SysML meta-model for the functional part.                                                                           | 23 |

| 3.6  | Sequence of mapping operation calls within the QVTo transformation entry point.                                         | 24 |

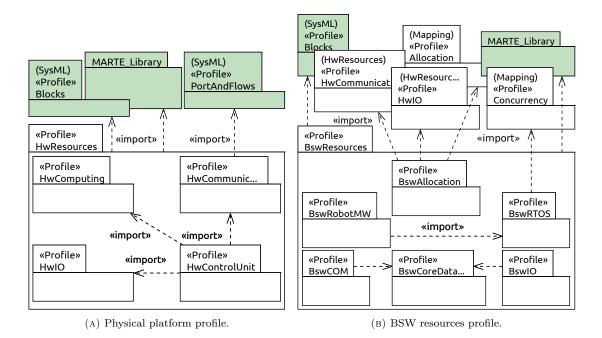

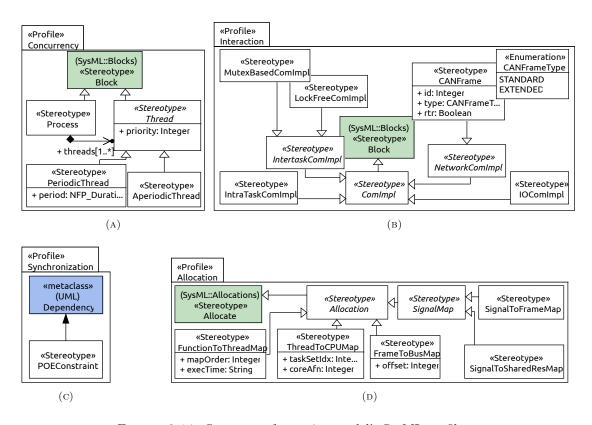

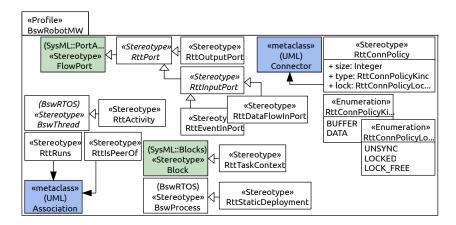

| 3.7  | SysML profiles for the execution platform with their dependencies.                                                      | 26 |

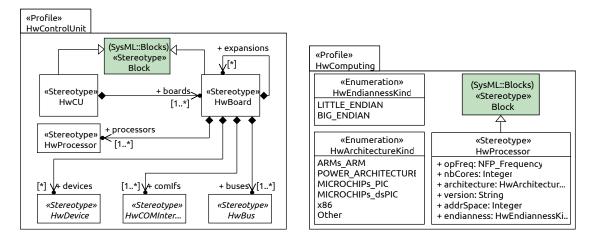

| 3.8  | HwControlUnit model's structure.                                                                                        | 27 |

| 3.9  | HwComputing model's structure.                                                                                          | 27 |

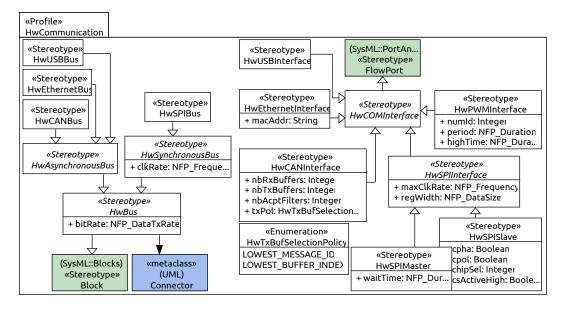

| 3.10 | HwCommunication model's structure.                                                                                      | 27 |

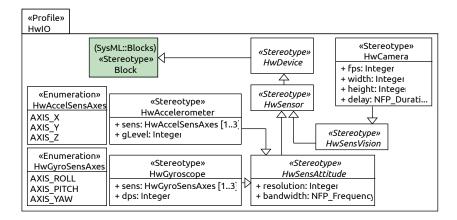

| 3.11 | Portion of HwIO model's structure.                                                                                      | 28 |

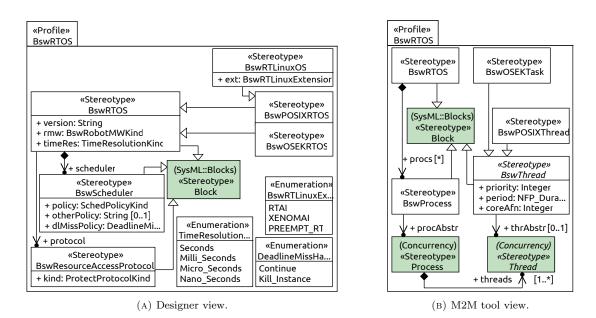

| 3.12 | BswRTOS model's structure.                                                                                              | 29 |

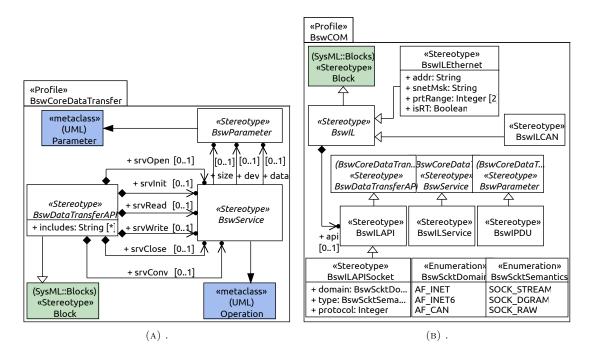

| 3.13 | Portion of BswCoreDataTransfer and BswCOM models structures.                                                            | 30 |

| 3.14 | Structure of mapping model's SysML profiles.                                                                            | 31 |

| 4.1  | Heterogeneous model integration and code generation by the framework tools.                                             | 36 |

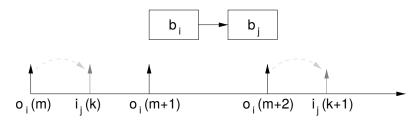

| 4.2  | Execution of a pair of connected blocks with direct feed<br>through according to the SR semantics $(i_j(k) = o_i(m))$ . | 38 |

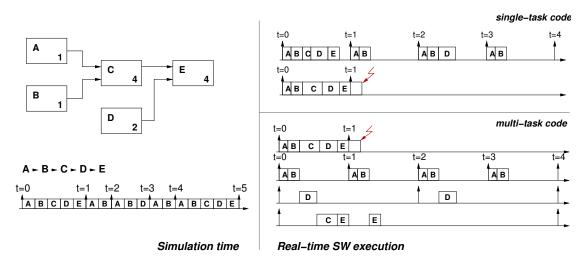

| 4.3  | Evaluation of blocks at simulation time and at runtime (single- and multi-task implementations).                        | 38 |

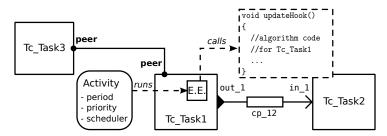

| 4.4  | Schematic representation of deployed Orocos-RTT components.                                                             | 40 |

| 4.5  | BswRobotMW model's structure.                                                                                           | 40 |

| 4.6  | Structure of Mapping::Synchronization package (extends that of Figure 3.14c).                                           | 41 |

|      |                                                                                                                         |    |

#### LIST OF FIGURES

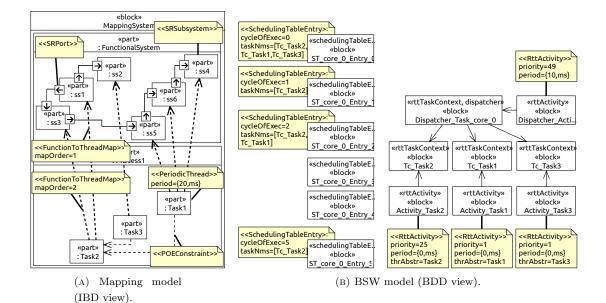

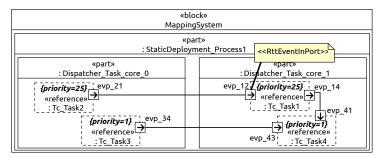

| 4.7  | Mapping model and automatically-generated BSW model representing the deployment onto a single-core processor.                                                                                               | 42 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

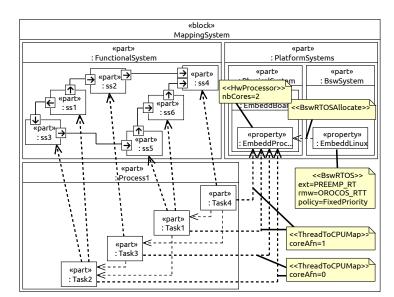

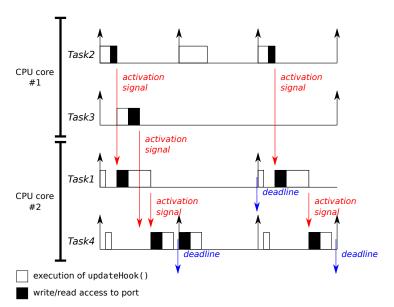

| 4.8  | Mapping model and automatically-generated BSW model describing the deployment of subsystems and threads onto a dual-core processor.                                                                         | 43 |

| 4.9  | Threads activation constraints in the dual-core architecture.                                                                                                                                               | 44 |

| 4.10 | Synchronization between producer/consumer Orocos-RTT components on a dual-core architecture.                                                                                                                | 44 |

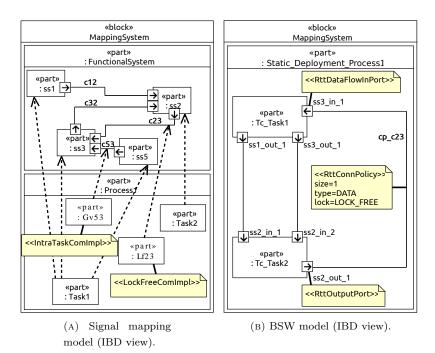

| 4.11 | Mapping model of functional communication links into signal variables (ComImpls), and automatically-generated BSW model.                                                                                    | 46 |

| 4.12 | Automatically-generated code for the platform-dependent realization of functional links.                                                                                                                    | 47 |

| 5.1  | T-Res in a Simulink-based PBD-like flow for real-time distributed embedded control systems development.                                                                                                     | 50 |

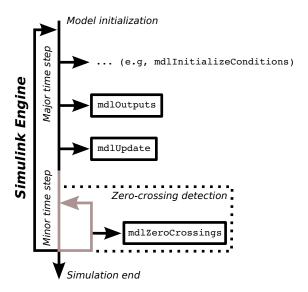

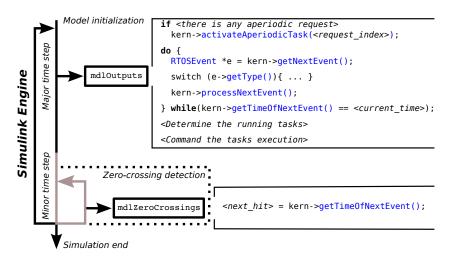

| 5.2  | Simplified view of S-function callback methods invoked by the Simulink engine during the simulation loop <sup>1</sup> .                                                                                     | 51 |

| 5.3  | Execution model of a simulated real-time task in Simulink.                                                                                                                                                  | 53 |

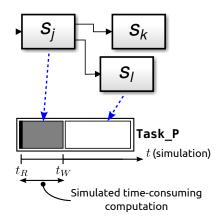

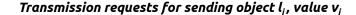

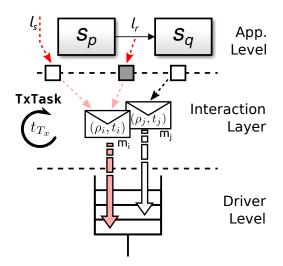

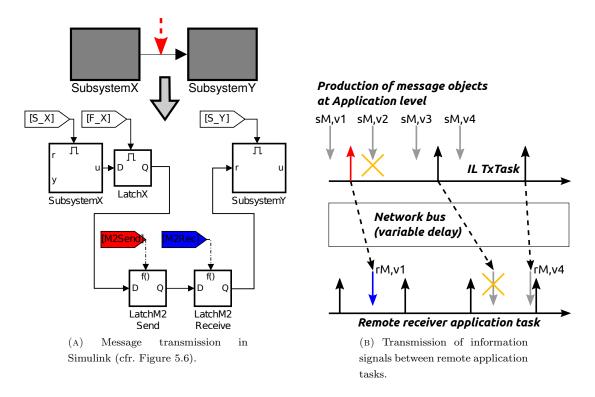

| 5.4  | Timing for the transmission of periodic mode messages objects.                                                                                                                                              | 55 |

| 5.5  | The middleware task TxTask executes with period $t_{T_x}$ , reads message objects and enqueues messages at the driver level.                                                                                | 55 |

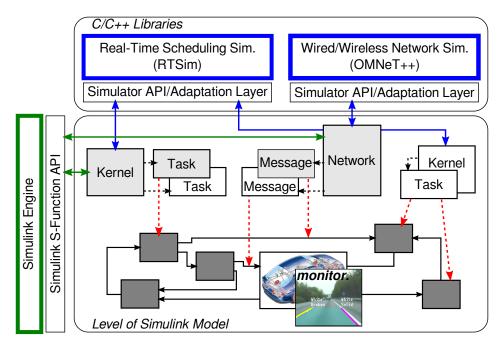

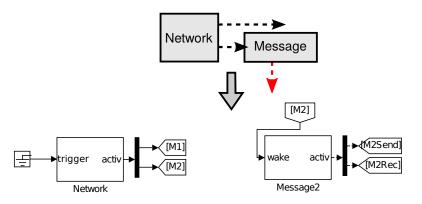

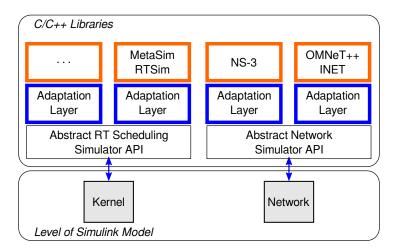

| 5.6  | Co-simulation of the functional controls (e.g., ADAS, dark-gray blocks), the plant (car) and the task scheduling and network communication parts (light-gray/white blocks), in a simplified representation. | 57 |

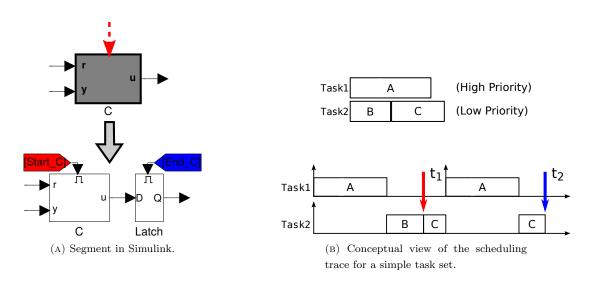

| 5.7  | Simulink implementation of time-consuming task computations execution model.                                                                                                                                | 58 |

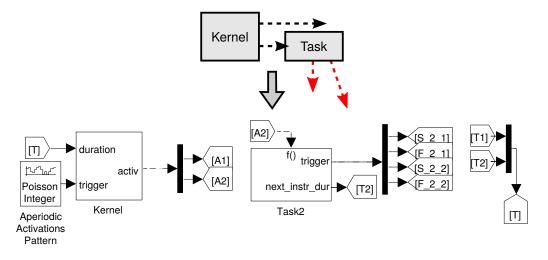

| 5.8  | Instances of T-Res blocks for the representation of kernel and tasks (bottom side), with respect to the simplified view in Figure 5.6 (top side).                                                           | 59 |

| 5.9  | Simulink implementation of finite-communication time network execution model.                                                                                                                               | 61 |

| 5.10 | Instances of T-Res blocks for the representation of network and messages (bottom side), with respect to the simplified view in Figure 5.6 (top side).                                                       | 62 |

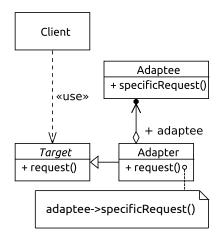

| 5.11 | Extensible architecture for interfacing T-Res with other platform DES simulators (closer view of top side of Figure 5.6).                                                                                   | 63 |

| 5.12 | Implementation of software architecture of Figure 5.11 using the object adapter design pattern.                                                                                                             | 63 |

| 5.13 | Simulation loop of Kernel S-function (pseudo-code).                                                                                                                                                         | 64 |

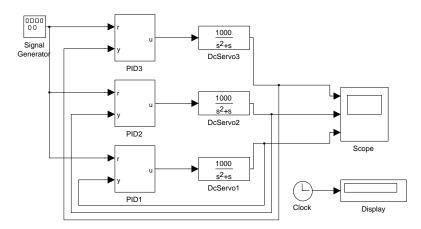

| 5.14 | The application example from TrueTime $[\mathbf{CHL^{+03}}]$ , PID control of three DC-servo systems.                                                                                                       | 65 |

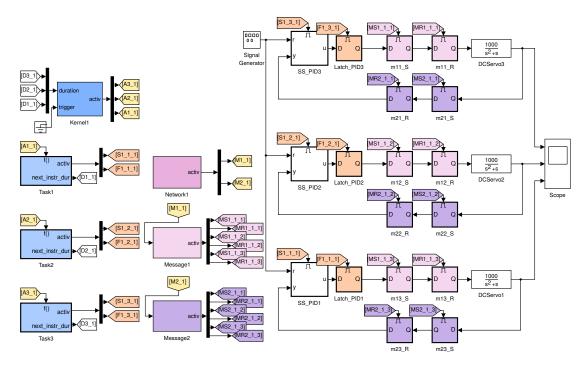

| 5.15 | Simulink model of DC-servo control system with back-annotations.                                                                                                                                            | 66 |

xiv

|      | LIST OF FIGURES                                                                                                                                   | xv |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

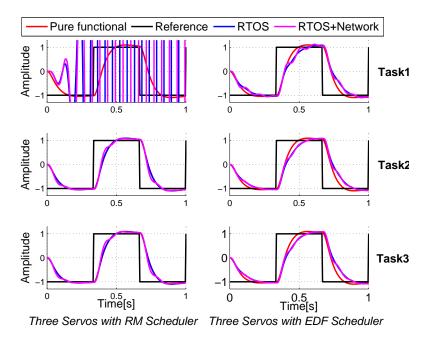

| 5.16 | Verification of DC-servo control system back-annotated model.                                                                                     | 67 |

| 5.17 | The IRIS quadrotor (left) and the PX4FMU Autopilot (right)                                                                                        | 68 |

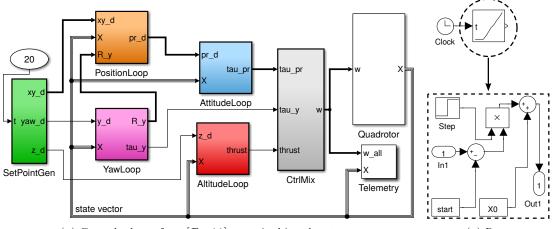

| 5.18 | Models used for the quadrotor flight-control scheme.                                                                                              | 68 |

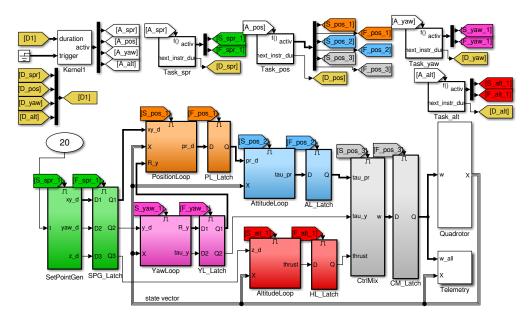

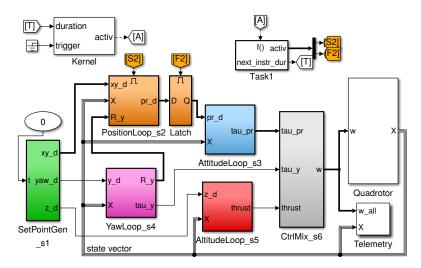

| 5.19 | Attitude control with models of RT kernel and tasks from T-Res.                                                                                   | 69 |

| 5.20 | Definition of type and timing properties of tasks.                                                                                                | 70 |

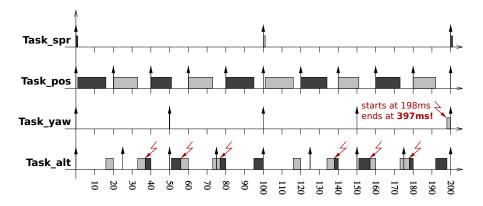

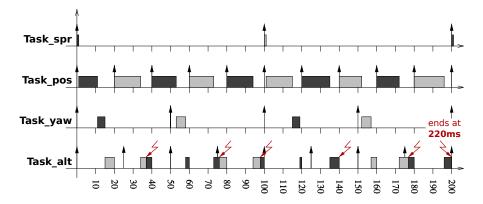

| 5.21 | Execution trace of FP#1 ( $200ms$ ), clearly showing that the task-set is non-schedulable.                                                        | 71 |

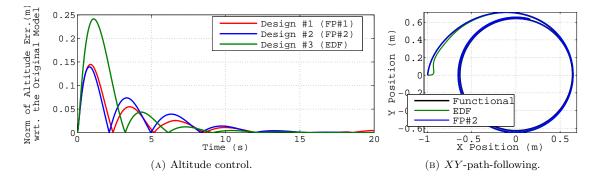

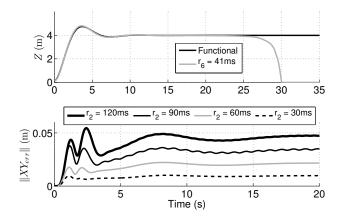

| 5.22 | Simulation results of first candidate design solution (FP#1), with respect to the control performance of model of Figure 5.18a (Functional).      | 71 |

| 5.23 | Execution trace of FP#2 (200ms): task-set is again non-schedulable.                                                                               | 72 |

| 5.24 | Simulation results of refined candidate design solutions (FP#2 and EDF), with respect to the control performance of model of Figure 5.18a.        | 72 |

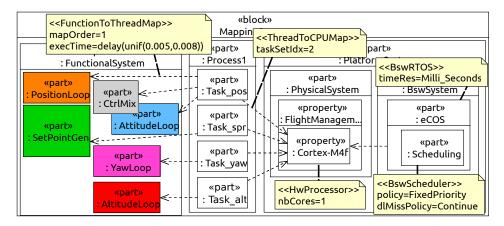

| 5.25 | SysML IBD describing the deployment of quadrotor's control functions and threads onto the single-core FMU board running a FP real-time scheduler. | 73 |

| 5.26 | Acceleo instructions for the generation of the Kernel block.                                                                                      | 74 |

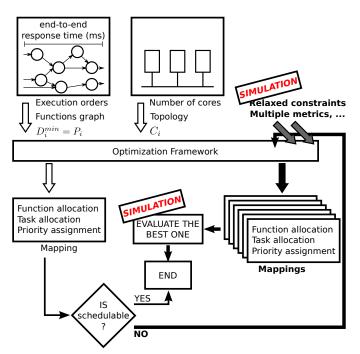

| 6.1  | Flow of the simulation-driven automated software synthesis process.                                                                               | 78 |

| 6.2  | The T-Res setup to evaluate the maximum acceptable delay for $f_2$ .                                                                              | 86 |

| 6.3  | Values of delays for $f_6$ (top) and $f_2$ (bottom) for which the performance is                                                                  |    |

|      | significantly compromised.                                                                                                                        | 86 |

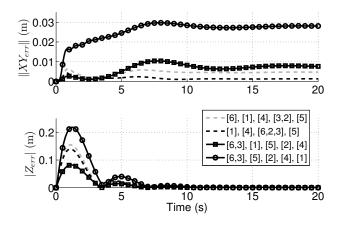

| 6.4  | Difference with respect to ideal case.                                                                                                            | 89 |

| 6.5  | $R_{od}$ model, comparison of task configurations and optimization metrics ( $U = 92\%$ ).                                                        | 90 |

## List of Tables

| 3.1 | Transformation rules for the Subsystem EClass and its EAttributes.          | 23 |

|-----|-----------------------------------------------------------------------------|----|

| 3.2 | Transformation rules for the Port EClass and its EAttributes.               | 25 |

| 3.3 | Transformation rules for the Signal EClass and its EAttributes.             | 25 |

| 6.1 | Subsystem names and corresponding function names for the quadrotor example. | 85 |

| 6.2 | Case study configurations for the design exploration.                       | 85 |

| 6.3 | Table of all computed mappings.                                             | 88 |

#### CHAPTER 1

## Introduction

#### 1.1. Cyber-Physical Systems (CPS)

Cyber-Physical Systems (CPS) integrate computation, networking, and physical processes. The physical process, or plant, is the physical part of the CPS. Embedded computers and networks are the cyber part. The plant is the *controlled system* and may include mechanical parts, human operators, etc. The cyber components *monitor and control* the plant.

Robotics is one of the most immediate applications of CPS, with future robots that are expected to move out of structured environments and cooperate extensively with humans in homes, offices, and novel industrial facilities designed for flexible manufacturing. Not only this, but also robotic-assisted surgery, autonomous driving and flight-control of Unmanned Aerial Vehicles (UAVs) are further emerging trends for CPS applications. Besides robotics, CPS have applications in domains such as agriculture, energy, defense, aerospace and building. Rajkumar *et al.* [**RLSS10**] describe CPS as *the next computing revolution* and discuss some technical challanges for their widespread adoption. Lee *et al.* [**L**<sup>+</sup>] provide a interesting conceptual chart that characterizes CPS, their core enabling technologies and applications.

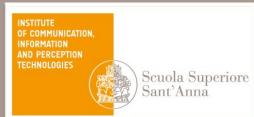

The typical realization of a CPS has the structure sketched in Figure 1.1a. Each embedded computer (Electronic Control Unit, or ECU) is made up of

- a set of hardware elements, including sensors, actuators, processors and network devices;

- an embedded software layer called Basic Software (BSW), including device drivers, operating system (OS), communication stack and middleware services.

Networked ECUs use sensors to measure the dynamics of plant. Processors execute the control logics; based on the sensors' data (feedback), they collaboratively determine the actions to influence the plant dynamics. Actuators perform these actions on plant.

The software algorithms that implement the control logics are called the *control software*. The control software is organized in layers, as shown in Figure 1.1b. Each software layer requires at least one type of real-time guarantees (as described in classical real-time textbooks, e.g., [**But11**]): *non-real-time, soft, hard real-time*. Note that most layers do not fall into exactly one category of the real-time guarantees.

In this work, we focus on *time-sensitive CPS control applications*, for which the correct functioning depends not only upon the logical correctness of control actions, but also upon the time in which these actions are performed. Control software is implemented as a set of tasks executed periodically within timing constraints (deadline or latency) and exchanging messages on networks.

FIGURE 1.1. CPS: typical realization and real-time guarantees of control software stack.

Broenink *et al.* [**BN12**] give a clear characterization of real-time embedded control software stack, which is summarized as follows. Time-sensitive applications/systems are operated by software at *supervisory, sequence* and *loop control* level. The *loop control* is at the lowest level, and is the software part that commands actuators. It is usually classified as hard real-time. The *sequence control* layer is a "task-level" controller that computes the set points for the loop controllers. Sequence control runs at a lower frequency than loop control. It can be classified either as hard or soft real-time, depending on application requirements. The *supervisory control* layer is a "strategy" controller. It instructs the sequence controller with the next task. Its calculations may take considerable amount of time and is typically classified as soft real-time.

For a robotic arm, an example of loop control is the (digital) Proportional-Integral-Derivative<sup>1</sup> (PID) controller to follow voltage/current setpoints for motor driving. Inverse dynamics or other PID controllers compute the setpoints for the lower-level PIDs from desired motion trajectories. These are examples of sequence controllers. If the arm is in close interaction with a human operator, reaction strategies upon unexpected collision or active control of arm's mechanical compliance will also be included in the computations of setpoints. The desired motion trajectories are computed by supervisory controllers performing, e.g., visual tracking, obstacle detection and collision avoidance tasks.

#### 1.2. Current Design Workflows

#### V-Shaped Lifecycle

The traditional real-time embedded system development process follows the standard Vshaped lifecycle. V-cycle splits the product development process into a design and an integration phase. Instead of moving down in a linear way, the process steps are bent upwards after the implementation. Each phase of the development life cycle has its associated phase of testing.

<sup>&</sup>lt;sup>1</sup>https://en.wikipedia.org/wiki/PID\_controller

While the way the V-cycle is actually realized varies significantly among practitioners in embedded systems, a number of limitations are common to all realizations. First, a very small amount of Verification and Validation (V&V) is performed that is supported by formal methods, model checking or other similar techniques. Timing verification starts after implementation and integration, with all the negative consequences this entails (issues due to timing are difficult to detect and even more difficult and expensive to fix). Second, the transition between the different stages requires careful manual inspection and cross-checking, and this is frequently error-prone. Third, it produces inefficient testing methodologies.

#### Multiple-V-Shaped Lifecycle

The *multiple-V-shaped lifecycle* addresses the above issues. It is developed in a sequence of three consecutive V-shaped development cycles (model, prototypes, and final product). The first V covers the definition and simulation of the overall system functionality. Software-in-the-Loop simulation is the primary methodology applied, and implementation aspects (including the time-triggered nature of the application) are not considered. The second V is characterized by rapid prototyping based on Hardware-in-the-Loop simulation. This phase covers the mapping of application tasks to computer nodes and the determination of among messages nodes. The third V addresses the system development for the final target hardware.

Gaps among V-cycles are the major drawbacks of multiple-V-cycle. There is a gap between the first and the second V: a distributed control application running stable at the first V might experience excessive delay due to message passing between computer nodes and fail (i.e., provide unacceptable Quality-of-Service or even exhibit unstable behavior) at the second V. There is a gap between the second and the third V: deadlines met by the oversized prototypical hardware (second V) might not be met on the target (third V).

#### 1.3. Platform-Based Design (PBD)

*Platform-Based Design* (PBD) originates from Electronic Design Automation (EDA) industry, where it is in use since some years. In the embedded systems industry, it has been promoted and advocated by A. Sangiovanni-Vincentelli [**SV02**]. Further literature references on this subject include [**SSVDB+05**, **B+06**, **DNSV10**]. The application of PBD to the development of complex CPS is introduced in [**SV07**] and recently discussed in [**SVS14**].

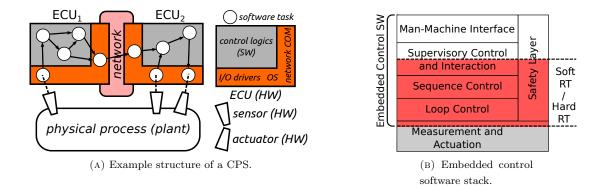

PBD introduces the concept of platform for virtual exploration in which some abstraction of the execution infrastructure is used in the earlier phases of the design flow in support of the exploration. In fact, PBD enables a *multi-level virtual exploration*. The rationale behind this design approach is that there is no reason to require that all parts of a system be explored simultaneously with the same level of granularity. The PBD cycle is a sequence of tool-assisted stepwise refinements that go from the initial specification towards the final implementation using models of platform at various level of abstraction.

*Platforms* are libraries of model components representing the design space that can be explored. For the design of CPS, libraries contain (at different levels of abstractions):

FIGURE 1.2. The PBD concept (reproduced from [DNSV10]).

- models of computational components that carry out the appropriate system functionality;

- models of architectural elements that represent the execution medium, such as microprocessors, memories, networks, sensors, actuators;

- models of execution software layers, that abstract the architectural elements to high level interfaces (APIs) that computational components can use.

Each element has a characterization in terms of performance parameters together with the functionality it can support. The selection of a particular collection of library components whose parameters are set defines a *platform instance*, i.e., a potential design solution at the level of abstraction the platform represents.

For every abstraction level, there is a set of methods used to map the upper level platform into an instance of the lower platform and propagate constraints (top-down process), and a set of methods used to estimate performances of lower level abstractions and to build (or refine) an upper level platform (bottom-up process). PBD is meet-in-the-middle process, as it can be seen as the combination of these two efforts (top-down and bottom-up), as shown in Figure 1.2a. The Figure shows that if designers are given a system platform, then several applications can be mapped into it and the parameters obtained by the design space export can be used to estimate the performance of the application onto the platform of choice. By the same token, if the application space is known, then the platform instance could be optimized according to the needs of the application space.

The mapping can be performed to optimize cost, timing constraints, energy consumption, reliability, etc. Figure 1.2b visualizes the refinement process. The mapped functionality of the system to be designed becomes the "function" at the lower level of the refinement. Another platform is then considered side-by-side with the mapped instance. This process is applied at all

levels of abstraction, and the process is iterated until all the components parameters are fully instantiated in their final form.

One important characteristic that makes PBD particularly suitable for the design of complex CPS is that it accounts for the interplay of top-down constraint propagation and bottom-up performance estimation. Another key benefit of adopting the PBD methodology is the elimination of costly design iterations (short time-to-market cycles), because PBD is a structured methodology that limits the space of exploration, and fosters design re-use of hardware and software at all abstraction levels.

#### 1.4. Research Objectives

The complexity of CPS poses significant challenges for their design and verification. This thesis aims to contribute to the ongoing discussion on how to deal with this complexity by applying the methodological framework of Platform-Based Design (PBD) to the development and deployment of complex, time-sensitive control applications for CPS.

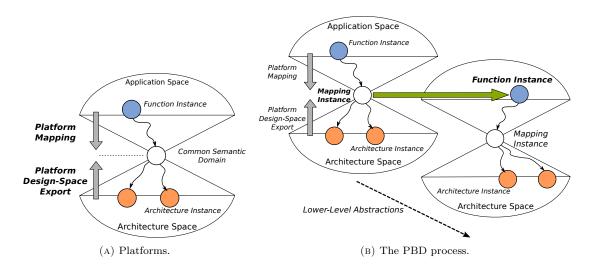

The PBD approach is completely general. It fosters a virtual exploration of the system design space on multiple levels and enables the specification of multiple goals for the exploration process. To put this work into a context that otherwise would be intractable in the most general case, we focus on the *three levels* that are of most immediate interest in the majority of instances of CPS design. These levels are the functional and the architecture platform layers, represented as the two cones in Figure 1.3, and the mapping layer, represented as the vertex of the two cones in the same figure. The mapping defines a software-architecture layer of tasks and communication resources that define the implementation of the (control) functionality on top of the architecture platform. The importance of these platform levels derives from the fact that most of the critical design choices are taken in the early stages of the design, and misconceptions in these stages produce costly and time-consuming re-design cycles. With a PBD approach considering those levels, fair exploration of design space can be performed, since crucial aspects such as functional specifications (of control) and their implementation characteristics are both handled formally and early in the design process.

We assume that functionality is modeled using *Synchronous-Reactive (SR) models*, that dominate the market of embedded control application design and on which widely used products like Simulink and SCADE (commercial) and Scicos (open-source) are based.

Finally, the gray arrow in Figure 1.3 indicates that we restrict our focus to *timing issues* as the primary design concern.

The model-driven approach of PBD is extremely flexible. It can serve as the backbone for the definition of a design flow where models from different (standard) tools are shared and the integration effort is reduced. This is of paramount importance, especially in modern CPS, where applications are designed by teams of engineers with different specialties (control, software, firmware and hardware) which work together but use different modeling and development tools.

As model-driven approach that complies to principles of PBD, the design process proposed in this work must support the transition from the functional model directly to the code implementation. A fundamental part of this problem is to guarantee that the generated implementation

#### 1. INTRODUCTION

FIGURE 1.3. The levels of platform abstractions that are of concern in this thesis.

preserves the semantics of functional model. Designers must understand under what conditions this may actually happen, and they must also realize the implications of an incorrect implementation. If a semantics-preserving implementation of functionality is not achievable, can designers define an implementation in which delays are deterministic and added to the model? In general, the proposed design process must be supported by tools that enable designers to explore tradeoffs between additional delays, feasibility and control performances.

The definition of such a design process, with the corresponding models, methods and tools is a challenging task, and it was subject to ongoing work throughout the entire thesis. The following introduces the research issues defined as the basic building blocks towards the realization of a supporting framework for the design of complex, time-sensitive control applications for CPS.

#### **RI.1.** Models and abstractions for the verification of implementation properties

A prerequisite for adopting the PBD approach is the definition of a common semantic domain where the platform models and the mapping process (Figure 1.3) can be represented formally. Models and abstractions must be isolated from lower-level details but, at the same time, must provide enough information to allow accurate prediction of the properties of the implementation.

Because our primary design concern is on timing issues, platform models at the three levels (control functions, architecture and mapping) must formalize attributes related to time. The model of the functions must be complemented by the formalization of constraints such as end-to-end deadlines. The architecture and the mapping models must formalize the properties of computation and communication resources that have an impact on the timed execution of control functions. For the architecture model, this requires a detailed representation of the basic software (BSW) and of the execution hardware (HW). For the mapping model, it requires the description of activation policies and priorities of tasks and messages, and the worst-case blocking time on shared communication resources.

The formalization of time-related attributes in platform models enables designers to devise system properties such as schedulability and average-case performance, and is at the core of the design of time-sensitive control applications for complex CPS. This research issue is investigated in Chapter 3.

#### **RI.2.** Semantics-preserving application deployments

In modern CPS, system properties of control functions (e.g., stability at steady-state, overshoot and settling time during the transient phase) are verified on a model of functional components by simulation or model checking, or other formal means. These properties remain valid after the implementation provided that the refinement of functional model into executable code be performed in such a way that the original semantics is preserved. This is especially important in safety-critical applications, where software certification plays a key role.

When the functional model is a synchronous model (as we assume in this work), available commercial code generation solutions produce code implementations for a single-core execution, and under restrictive assumptions about the scheduling policy. Novel tools are needed that support the code-generation phase in a PBD flow for, at least, multi-core systems. This research issue is investigated in Chapter 4.

#### RI.3. Simulation tools to predict the system-level timing behavior

When the full preservation of functional model semantics cannot be guaranteed by the implementation, designers may resort to simulation to gather important information about the estimated impact of time delays on the control performances.

It is worth to make the clear statement on this scenario, that simulation alone is not sufficient to achieve software certification of implementation. But there exist numerous time-critical applications in many application domains of CPS that do not need to undergo a rigorous certification process, and for which predicting the system-level timing behavior (latencies and jitter) is a crucial competitive advantage for designers.

Tools are needed that enable such a kind of analysis when the functional model is a synchronous model. Moreover, these tools must comply to the key principle of PBD, i.e., the separation of concerns between control functions and architecture. Separation of concerns requires that model artifacts representing the software architecture model be added to the functional model as annotations through automatic transformations. This research issue is investigated in Chapter 5.

#### RI.4. Automatic software architecture configuration

The mapping of the functional model into the execution platform is a crucial step in the PBD process. In fact, several possible options exist for the definition of software architecture (mapping) once the control functionality and the architecture platform are defined. In distributed architectures, the design of the software architecture is a very complex task that may require several iterations and is often delegated to the most experienced designer.

The procedure for (software) architecture selection and evaluation is today a "what-if" iterative process [SVDN07]. First, the designer provides an initial set of architecture options. Then, the designer uses a set of metrics to evaluate if the architecture options fit to the exploration

#### 1. INTRODUCTION

goals. If the designer is not satisfied with the result, a new set of candidate architectures is evaluated. The iterative process continues until a solution is obtained.

Because the search space is extremely large in most cases, it is very likely that designers have to settle for solutions not only not optimal, but possibly far from optimality. To improve the current situation, automated tools should provide guidance in the definition of the optimal configuration of the software architecture when evaluating an execution platform option, and in the analysis of the results. This research issue is investigated in Chapter 6.

#### 1.5. Thesis Outline

Each of the core Chapters 3–6 is based on peer-reviewed conference or workshop papers. These Chapters do not include discussions of related work, because all the literature review relevant to the research objectives of this thesis is discussed in Chapter 2.

Chapter 3 defines formally the process flow and introduces models and abstractions for the three levels of platform, namely, functional (synchronous models), architecture and mapping. This chapter lays the groundwork for successive Chapters, that present tools for timing-analysis and code-generation which operate on these platform models.

Chapter 4 introduces models and a formal process (code-generation) enabling the implementation of (robot) control applications with the preservation of the SR flows on single-/multi-core computing architectures. The target of the code-generation process is the real-time capable, widely used robotic middleware Orocos-RTT [**Bru**].

Chapter 5 describes models and automated tools to integrate the simulated execution of system scheduling (of real-time tasks and network messages) with control simulation, allowing for the analysis of the impact of computation and communication delays on control performance. The attitude control of a simulated Unmanned Aerial Vehicle (UAV) is used as case study.

Chapter 6 presents a simulation-driven optimization process for the automated synthesis of the software system architecture. The process aims at exploring the interplay between the control performance and the real-time behavior under relaxed constraints (e.g., task deadlines), and at evaluating the quality of different software implementations. The method is applied to a UAV case study.

Chapter 7 concludes the thesis, by summarizing contributions, impact and limitations of this work, as well as suggesting opportunities for future research.

#### CHAPTER 2

## Methods and Tools for System-Level Modeling and Design

#### 2.1. Introduction

This Chapter provides a review of existing methods and tools related to the research objectives formulated in Section 1.4. We introduce the methodologies and the supporting modeling languages and simulation tools that are today in use in the industrial domain or explored in the academic-research domain. We discuss their strengths and weaknesses and identify the basis for the proposed system-level design flow described in the next Chapter.

#### 2.2. Model-Based Design (MBD)

The Model-Based Design (MBD) approach enables behavioral modeling based on a mathematical formalism and executable semantics. In a mathematical-based language, the Model of Computation (MoC) describes the semantics of computation and communication among model elements, and assumes paramount importance. A wide variety of formalisms exist, as reported in [LSV+98].

In the domain of CPS control applications development, MBD is the reference approach for the analysis of the system, its verification by simulation, the documentation of the design and the automatic generation of a code implementation. Functional models are based on a Synchronous-Reactive (SR) execution paradigm. Examples of available commercial tools are Simulink [**Theb**] (which is the *de-facto standard*), SCADE [**Est**] and LabVIEW [**Nat**]. Open source and research tools include Scicos [**INR**]/Xcos [**Sci**] and Ptolemy [**EJL**+03] (which supports multiple MoCs). These tools are feature-rich and allow the modeling of continuous-, discrete-time, and also hybrid systems. The control functionality is typically defined using dataflow formalism (possibly in combination with an extended finite-state machine formalism). The controls are simulated against a model of the controlled system (plant), and then validated. The development of complex functionality may require several iterations, but the availability of a virtual simulation environment allows to speedup the verification of each solution (as opposed to traditional testing) and to verify scenarios that would be impractical or even impossible to setup on the actual system.

A common limitation to most commercial modeling and simulation tools is that the functionality is represented in abstract terms, that is, independent from the execution platform that will support the execution of the controls as a set of software tasks and network messages. A sound development methodology should ensure that the computation and communication delays that occur when the system is implemented on a (possibly distributed) execution architecture with finitely available resources preserve the execution assumptions that are part of the simulated (and verified) model. 2. METHODS AND TOOLS FOR SYSTEM-LEVEL MODELING AND DESIGN

Sometimes, a semantics preserving implementation is not feasible for the selected execution platform, and the only option is to account for the computation and communication delays in the simulation.

Verifying the preservation of the SR semantics or estimating the delays requires the construction of a model of the execution platform and providing an assumption on how the functionality will be implemented on the computation resources.

In addition, in a sound model-based flow, the software implementation of the model should be automatically generated by a model compiler. This is desirable not only for improving efficiency, but for guaranteeing that no errors are introduced in a manual coding stage. Unfortunately, current code generators only produce a code implementation for a single core execution, and under restrictive assumptions about the scheduling policy.

#### 2.3. Model-Driven Engineering (MDE)

Model Driven Engineering (MDE) is a software development approach that promotes the use of models and their transformations in the software development process. The central idea in MDE is the definition of domain-specific models (called *meta-models*) that capture the aspects relevant to a particular domain. In other words, domain-specific models represent the knowledge and activities that govern a particular application domain. Concrete models conformant to the meta-model can then be analyzed, validated, transformed and executed.

MDE is a modeling *paradigm*. One of most relevant standardization efforts of it is the Model Driven Architecture (MDA) initiative [(OMb] by the Object Management Group (OMG). MDA prescribes a design process in three stages. First, a Platform-Independent Model (PIM) defines the system functionality independently of the software platform it will execute onto. Next, the PIM is transformed to the Platform-Specific Model (PSM) by means of a Platform-Definition Model (PDM). Finally, the PSM is transformed in a Platform-Specific Implementation (PSI). The first transformation is *Model-to-Model* (M2M): it transforms the PIM (source model) into a model of the software execution platform (target model). The second transformation is *Model-to-Text* (M2T), because it transforms the PSM into final code implementation (PSI).

OMG defines several other standards to effectively support MDA. The Meta-Object Facility [(OMg] (MOF) specification describes the meta-meta modeling language and the rules that specify meta-models. The Query/View/Transformation [(OMe] (QVT) standard defines M2M transformation languages, which operate on models conform to MOF. A key component of QVT is the Object Constraint Language [(OMd], (OCL) that allows the specification of constraints on models. M2T transformations are standardized separately as MOF Model to Text Transformation Language [(OMc] (MOFM2T).

The Unified Modeling Language [(**OMh**] (UML) defines diagram types for modeling a number of software aspects, including *behavior*. However, UML lacks of a rigid semantic formalization, and only recently OMG has released a behavioral semantics specification with the foundational UML [(**OMf**] (fUML) and Action Semantics language [(**OMa**] (ALF).

Within MDE paradigm, we can distinguish two modeling approaches: profiling and metamodeling. *Profiling* is the mechanism standardized by the OMG that allows adaptation of the UML meta-model for a specific application domain. *Stereotypes* and their attributes enable the representation of concepts for that specific domain. Today, many profiles exist for numerous domains. The System Modeling Language [**Obj12**] (SysML) and the Modeling and Analysis of Real-Time and Embedded Systems [(**OM11**] (MARTE) profile are relevant in the context of this work.

SysML is a general-purpose modeling language for systems engineering applications. SysML offers concrete advantages over UML for tasks like capturing system requirements and specifying quantitative constraint on the system. However, its behavioral semantics is not completely and formally specified (like for UML).

MARTE introduces UML extensions describing a variety of non-functional properties, and aims to provide support for specification, design, and verification/validation of real time and embedded systems.

*Meta-modeling* is the approach of defining a new meta-model from scratch. As of today, the Eclipse Modeling Framework [**Ecla**] (EMF) is the most widespread framework that supports meta-modeling. EMF enables the definition of custom metamodels using its Ecore meta-modeling language, which is the de-facto reference implementation of (a subset of) OMG's MOF<sup>1</sup>.

#### 2.4. Frameworks for Heterogeneous-Model Integration

In agreement with the principle of separation of the functional and architecture design concerns, and with respect to the subject of heterogeneous models integration, several approaches, methods and tools have been proposed. GME  $[\mathbf{KML^+04}]$  and MetroII  $[\mathbf{DDM^+07}]$  propose the use of a general meta-model as an intermediate target for the model integration. However, they do not provide simulation capabilities or a code generation path for distributed implementation based on open source tools and open standards.

Raghav et al. [**RGR**<sup>+</sup>10] and Hugues et al. [**HZPK08**] proposed two similar MDA methods for describing the functional behavior according to a reference architecture and then comparing the deployed system with respect to the reference to check whether the performance (delay) target is guaranteed.

GeneAuto [Gen], ProjectP [Pro], the Rubus Component Model [HMTN<sup>+</sup>08] and AADL [AAD] put emphasis on the modeling of task sets and their interactions and the code generation infrastructure, without including simulation capabilities or an explicit formal metamodel for the internal behavior of tasks.

#### 2.5. System-Level Approaches in Automotive and Robotics

#### Automotive (AUTOSAR)

AUTOSAR [AUT] is a development partnership of automotive OEMs (Original Equipment Manufacturers) and suppliers. The partnership aims to develop an open industry standard for automotive software architectures. The standard covers all software levels, from the BSW to the

<sup>&</sup>lt;sup>1</sup>https://jaxenter.com/eclipse-modeling-framework-interview-with-ed-merks-100007.html

specification of platform-independent application-level components. A meta-model formalizes all the definitions provided by the standard.

AUTOSAR is perhaps the most successful application of MDA paradigm in the industry. The AUTOSAR standard defines a virtual integration environment for the software components and a separate model for the distributed execution architecture, later merged in a deployment stage supported by tools. However, the current implementation of the standard lacks the support of a formal MoC, and hence is not suitable for the early-stage control validation. Also due to this, the integration of AUTOSAR with MoC-based executable languages (e.g., Simulink) presents several difficulties.

#### Robotics

In robotics, the most common design paradigm for application development is the componentbased SW engineering. Frameworks such as ROS [**Ope**], OpenRTM-aist [**AIS**] and Orocos-RTT [**Bru**] act as middlewares, providing abstractions to encapsulate active control threads and communications among them. Orocos-RTT is specifically oriented toward programming and executing component-based applications on top of *Real-Time* Operating Systems (RTOSes) and relies on *lock-free* communication to guarantee a deterministic execution time for all in-process inter-component data exchange.

However, this situation is changing and MDE approaches are becoming increasingly popular. In the last few years, several MDE Integrated Development Environments (IDEs) and Domain-Specific Languages (DSLs) have been made available. BRIDE is an IDE based on Eclipse developed in the BRICS project [web]. It targets the automatic generation of platform-specific code for component-based frameworks from a graphical (abstract) model of the system architecture and its SW components (the BRICS Component Model [BKH<sup>+</sup>13]). BRIDE uses model-to-model (M2M) transformations to generate framework-specific code for the communication, configuration, composition and coordination of ROS and Orocos-RTT components. The declarative description of robotics architectures and SW deployment using a DSL is described in [HGS<sup>+</sup>13] with a hierarchy of architectural concepts for HW and SW, inspired by AADL [AAD]. However, the properties of HW and SW that define the timing behavior of components are not included. The SmartSoftMDSD toolchain [SSBK10] supports non-functional properties for design-time real-time schedulability analysis. The framework allows the graphical modeling of applications and provides M2M transformations to construct a platform-specific model for schedulability analysis using Cheddar [SLNM04].

Some IDE provide DSLs for the algorithmic description of behaviors.  $V^3CMM$  [AVCO<sup>+</sup>10] is a modeling language that provides a simplified version of UML activity diagrams, to model the sequential flow of execution within components. RobotML [DKS<sup>+</sup>12] is a DSL aiming at the design of robotic applications and their deployment to multiple target execution platforms (and simulators). It uses a specialization of UML state machines for the modeling of the behavior of generated component implementations. RobotML enables (simplistic) modeling of platform-specific non-functional properties of SW components, that are used to create models

for third-party real-time schedulability analyzers. Hence, it suffers the same drawbacks of the SmartSoftMDSD toolchain.

Virtual Path [NJH09] is a HW-SW co-Design method that includes Simulink in the development flow, to create executable models representing the controls. In [WNBG12], Wätzoldt *et al.* adapt the automotive toolchain to the development of robotic systems. The design methodology uses Simulink for the simulation of robot functionalities, and Embedded Coder for the generation of the implementation. AUTOSAR models and tools (e.g., SystemDesk [dSP]) are used to combine hard and soft real-time tasks in a system view and analyze the scheduling feasibility.

#### 2.6. Simulation of Platform's Delay Effects

Models can capture the architecture-level details and enable the study of system's timing behavior by means of timing analysis techniques (e.g., using MARTE). Another approach is simulation. Simulators can provide support for the evaluation of effects that computation and communication delays have on the performance of the system.

Network simulators can aid in the evaluation of communication delays (due to, e.g., message transmission). A large variety of simulation tools are available from the industry and the academia. Most of them are geared towards the use in a specific domain. NS-3 (Network Simulator) [NS-] and OMNeT++ [OMNa] are freely available discrete-event computer network simulators. They support several communication protocols and are extensible for the inclusion of new ones. In [MMT<sup>+</sup>] a simulation environment for CAN-Ethernet networks is presented as example of extension to OMNeT++.

Real-time scheduling simulators support the evaluation of computation delays (finite execution times, scheduling delays, etc). A huge number of projects target the evaluation of scheduling policies and the analysis of task implementations (more than 6 million hits when searching the keywords *Real-Time Scheduling Simulator* in Google). A necessarily incomplete list includes Yartiss [CFM<sup>+</sup>12], Storm [UDT10], ARTISST [DP02], Cheddar [SLNM04], Schesim [MSHT12], Stress [ABRW94].

Simulators must be used in conjunction with MBD tools that support the definition of control applications, to effectively support the designer in the architecture evaluation process. The following lists the possible options for use with Simulink.

#### **Options for Simulink**

#### Co-Simulation with Third-Party Programs

A number of research works address the problem of combined execution of Simulink together with an external program for network simulation. Relevant works on this topic include [HA04, Kac10]. They share the idea of using sockets (TCP/UDP) to establish a bidirectional communications between the two simulators. This requires the implementation of special coupling components, that slow down the simulation and realize the coordination between the simulators in ad-hoc fashion. Furthermore, these implementations are tied to the specific network simulator and are difficult to interface with others.

#### Co-Simulation with Ad-Hoc Implementations of Scheduling and Network Simulators: The TrueTime Toolbox

In Simulink, a possible solution for the simulation of platform's computation and communication delays is provided by the TrueTime toolbox [CHL+03]. TrueTime is already used by many research groups worldwide to study the (simulated) impact of lateness and deadline misses on controls. Relevant literature on this subject includes [ÅW11] and [CVMC11].

TrueTime enables the simulation of control functions considering their software task and message implementations, including scheduling and resource management policies. It provides two special-purpose Simulink blocks representing a model of multi-tasking real-time kernels and of a network, respectively. The kernel model supports many popular scheduling policies for single-core systems, such as Earliest Deadline First (EDF) and Fixed Priority (FP), including Rate Monotonic (RM). Presently, multi-core architectures are not supported. For what concerns the network standards, TrueTime supports Ethernet, CAN and FlexRay, and wireless network standards such as 802.11b WLAN and 802.15.4 ZigBee.

In TrueTime, the kernel models in fact a *computer node* together with A/D and D/A converters, external interrupt inputs and network interfaces. The corresponding block is configured via an initialization script (usually written in Matlab code), where a specific API is used by the designer to create tasks, timers and interrupt handlers and define the scheduling policy and the communication resources. The model of task code is represented by *code functions* that are written in either Matlab or C++ code. A TrueTime developer has two options: hand-code the control logic and lose availability of Simulink (control) toolboxes, or call external discrete-time Simulink models from within the code functions using a mechanism based on the MATLAB built-in operator sim() with several limitations. First, signal-generator blocks that use the simulation time and blocks for which it is not possible to specify the sample rate (e.g., the Discrete Derivative block) cannot be used. Second, data connections among Simulink models need to be implemented in code using a purposely offered API and the application of a TrueTime Scheduler to an already existing Simulink model of controls requires substantially rewriting, mixing the controller functionality, the model of the task set, the scheduler, and the physical execution platform. Finally, because of the monolithic architecture and the number of code artifacts that are needed for system configuration (e.g., initialization script and code functions), the current TrueTime implementation is hardly compatible with an automatic model generation and a M2M transformation flow.

#### Native Simulink Discrete-Event Simulation: SimEvents

SimEvents [**Thea**] is a commercial toolbox developed by The MathWorks, providing a discrete-event simulation engine and component library for Simulink. It enables event-driven communication modeling between Simulink components to analyze and optimize end-to-end latencies, throughput, packet loss, and other performance characteristics. SimEvents is modular and its component library comes with many blocks that allows the designer to customize processing delays, prioritization, and other operations, to represent systems that range from manufacturing processes, to hardware architectures and sensor/communication networks.

Because of its generality though, SimEvents does not provide an explicit model of task, realtime scheduler, network protocol or hardware component. They need to be built as libraries using blocks representing priority queues and servers.

#### 2.7. Discussion and Conclusions

Concepts and methodologies reviewed in Sections 2.2 and 2.3 can be summarized as follows. On one side, SR languages (e.g., Simulink) allow for the simulation of controller-plant interactions and behavioral code generation (of control), but offer no support for the representation of complex system architectural aspects and execution platforms. On the other hand, MDA languages are very good at representing architectural aspects, can be easily extended and provide mechanisms to transform models expressed in a language into another; but their behavioral semantics is weak (not completely and formally specified) and they are not suitable for modeling continuoustime systems. Their strengths and weaknesses are complementary. Therefore, *MBD and MDA approaches are good choices to form the backbone of the PBD design flow*.

Within MDA, MARTE is today the best option for the definition of distributed embedded systems with real-time constraints, although with some limitations. MARTE purposely lacks the complete specification of a number of HW and SW concepts, that is left up to model-library designers. However, when there is the intent of processing a model annotated with MARTE stereotypes to analyze it or to generate code/models from it, the introduction of new language constructs becomes necessary [SG14]. Moreover, MARTE defines a number of stereotypes to represent BSW concepts that are mostly cumbersome, come with a large number of properties and are quite difficult to be mastered by the system designer. As a result, this work requires *custom taxonomies of stereotypes extending MARTE*.

Despite much research, such an *integrated MBD/MDA framework*, based on SR and SysML/-MARTE models, is not ready available (Section 2.4). Among possible alternatives, the reviewed works that provide a clear separation of the functional and platform models (GME, MetroII) typically do not provide model-based simulation capabilities or a code generation path for distributed implementation based on open source tools and open standards. AUTOSAR (Section 2.5) does not have any feature for modeling the behavior of the functions. Therefore, an exetrnal tool or the actual code is needed for functional modeling. The same consideration holds for the majority of the frameworks today available for model-driven development in robotics. Those that provide support for behavioral modeling are based on UML and, consequently, model execution and simulation are tool-specific. Nearly all lack any kind of support for timing analysis. Others (e.g., SmartSoftMDSD) portray an approximate (and sometimes inaccurate) view of the schedulability problem as a binary decision process ("ok"/"not ok").

Finally, tools reviewed in Section 2.6 do not represent a viable solution to the problem of simulating computation and communication delays in SR models. This demands the development of a novel, modular and extensible co-simulation framework to be integrated in the proposed modeldriven flow.

#### CHAPTER 3

### **Design-Process Flow and Platform Meta-Models**

#### 3.1. Introduction

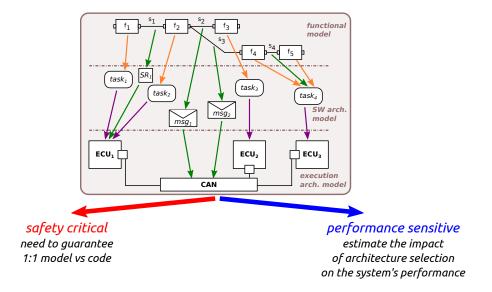

As model-driven approach that complies to principles of PBD, the design process proposed in this work integrates executable, synchronous models of control with structural models of the execution platform in a sequence of stepwise refinements from the initial specification towards the final implementation. The mapping of control functions to the platform is performed through an intermediate layer, in which functions are implemented by tasks and communication between components maps into local communication (internal or between tasks) and network messages. The top side of Figure 3.1) represents (conceptually) the process of mapping the functions model onto a model of the execution architecture through the intermediate SW architecture model.

Two major application scenarios are considered in this thesis, namely those of design of *safety-critical* and *performance-sensitive* systems. In both the scenarios, the use of models is a consolidated practice to improve the quality of the system and to speed-up the development process (albeit with several limitations). The link between the proposed PBD process and the application scenarios is visualized in Figure 3.1) (bottom side). The mapping model is represented as the *foundation* part in the successive refinement view of PBD for both the scenarios, since

FIGURE 3.1. Platform models, mapping process and application scenarios for the proposed design flow.

(A) Steer-by-Wire<sup>1</sup>

(B) Lane Departure Warning<sup>2</sup>

FIGURE 3.2. Examples of safety-critical and performance-sensitive systems in automotive.

only after mapping is described one can verify whether constraints on non-functional properties of the design are satisfied.

In safety-critical CPS, failure or malfunction may result in death or serious injury to people, loss of or severe damage to equipment, and/or environmental harm. Examples from the aerospace/automotive and robotics domains include X-by-Wire (e.g., Steer-by-Wire, Figure 3.2a) and physical Human-Robot Interaction (pHRI) systems, respectively.

Safety-critical systems demand precise guarantees that the final implementation will satisfy a number of properties, formally verified during the design phase with the use of model checkers or other formal means. They must pass thorough certification processes to be put in operation. Examples of safety standards are ISO26262 [Int], for road vehicles functional safety, and DO-178B [**RTC**], for SW considerations in airborne systems. Therefore, a process addressing their design at system-level must support the transition from the functional model directly to the code implementation in a way that the generated implementation is guaranteed to preserve the semantics of functional model (SR). This includes overcoming the limitations of current commercial code generation solutions, that, for synchronous models, can produce semantics-preserving code implementations only for a single-core execution, and under restrictive assumptions about the scheduling policy.

The other major application scenario for the proposed framework is that of *performance*sensitive systems design. This kind of systems are time-critical, i.e., subject to demanding timing constraints, and often have the potential for very high consequences of failure. In fact, in many cases the distinction between safety-critical and performance-sensitive systems is subtle, and mostly depends on whether the law mandates system designers to show compliance with an applicable (safety) standard. Examples from the automotive domain include Advanced Driver Assistance Systems (ADAS), such as Adaptive Cruise Control (ACC) and Lane Departure Warning (LDW) (Figure 3.2b) systems.

<sup>&</sup>lt;sup>1</sup>http://www.caranddriver.com/features/electric-feel-nissan-digitizes-steering-but-the-wheelremains-feature

<sup>&</sup>lt;sup>2</sup>http://www.continental-automotive.com/www/automotive\_de\_en/themes/passenger\_cars/chassis\_ safety/adas/

#### 3.1. INTRODUCTION

It is very common that performance-sensitive systems are classified as hard real-time systems. Therefore, their design is carried out according to the classical separation of concerns between the correctness of control functionality and the verification of the time properties of the computations.