## **WATERS 2011**

July, 5th - Porto, Portugal

Scuola Superiore Sant'Anna di Studi Universitari e di Perfezionamento

#### Tools for Real-Time and Embedded Systems An Integration View

Tommaso Cucinotta

Real-Time Systems Laboratory (ReTiS) Scuola Superiore Sant'Anna, Pisa (Italy)

SEVENTH FRAMEWORK

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

## Outline

# **Talk Outline**

- □ Introduction

- □ Selected Tools for RTES at the ReTiS

- → Scheduler for soft real-time VMs running on Linux/KVM

- → MetaSim / RTSim

- → ARSim

- → MCoreSim

- □ Selected Tools for RTES at Evidence s.r.l.

- → Scheduler for real-time embedded applications on Linux

- $\rightarrow$  RT-Druid

- → Erika

- Integration Efforts in Automotive (INTERESTED)Questions

3

## Introduction

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

## Introduction

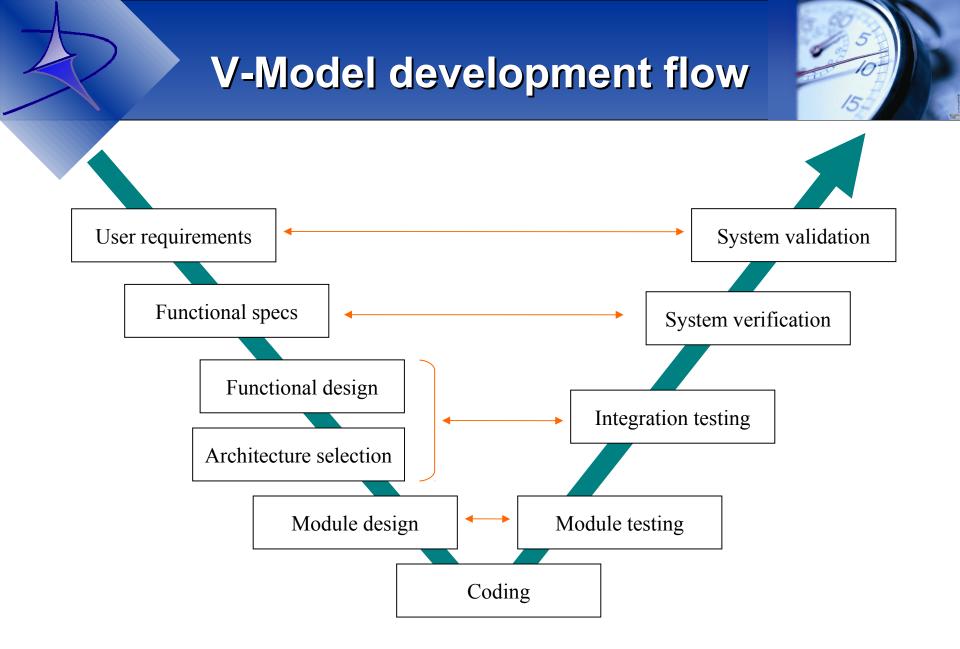

# **RTES Design & Development Challenges**

- Compliance of Design, Architecture, Implementation with Requirements

- □ Functional as well as non-functional correctness

- → Behaviour, timeliness, deadlines

- → Reliability

- → Guarantees of correctness (under any possible run-time condition)

- □ Composability of software components

- → Keeping under control timing interferences

- □ Mapping on multi-core and heterogeneous hardware

- □ Exploration of design space

## Introduction

# **RTES Design & Development Challenges**

- Compliance of Design, Architecture, Implementation with Requirements

- □ Functional as well as non-functional correctness

- → Behaviour, timeliness, deadlines

- → Reliability

. . .

- → Guarantees of correctness (under any possible run-time condition)

- □ Composability of software components

- → Keeping under control timing interferences

- □ Mapping on multi-core and heterogeneous hardware

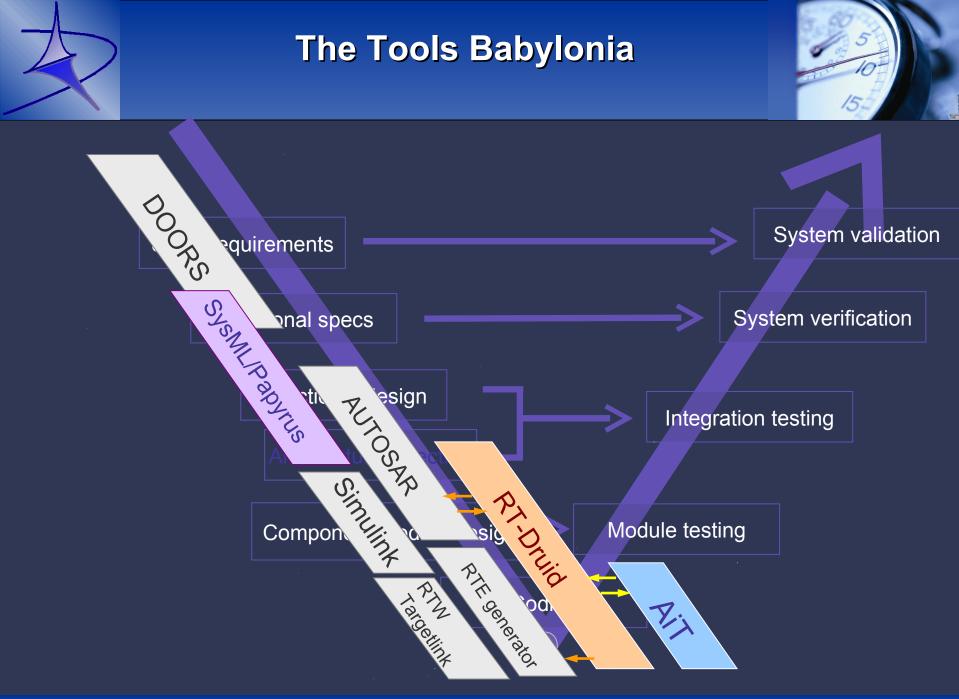

# **Appropriate Tools & Methodologies are needed**

#### **Problems**

- Heterogeneous models

- Interoperability issues (syntax)

- Integrability issues (semantics)

#### **Problems**

- Heterogeneous models

- Interoperability issues (syntax)

- Integrability issues (semantics)

#### But let's add some more tools before going on!

10

# **Tools for RTES at the ReTiS**

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

#### IRMOS Real-Time Scheduler

#### **Features at a glance**

- □ Resource Reservations

- → EDF-based scheduling (hard CBS)

#### Hierarchical scheduling

- → Multiple tasks attached to same reservation

- → POSIX Fixed Priority scheduling inside each reservation

#### □ Multi-processor reservations

- → Partitioned scheduling for improved efficiency

- → Migration of tasks among CPUs

#### Simple admission control

Interactive Realtime Multimedia Applications on Service Oriented Infrastructures

MD5

## IRMOS Real-Time Scheduler Design Goals

# **Replace real-time throttling Tight integration in Linux kernel**

Modification to the Linux RT scheduler

# Reuse as many Linux features as possible

- Management of task hierarchies and scheduling parameters via cgroups

- POSIX compatibility and API

# **Efficient for SMP**

Independent runqueues

Interactive Realtime Multimedia Applications on Service Oriented Infrastructures

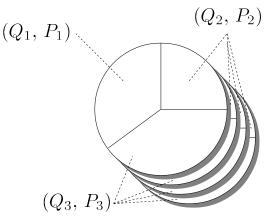

# Real-Time systems SIMulator (RTSIM)

# What is RTSIM ?

A collection of reusable C++ components for simulating realtime (control) systems

#### Features

- Task Model

- → Periodic, Sporadic, Aperiodic

- → Period, WCET, Deadline,...

- Multi-Core Support

- → Global/Partitioned Scheduling

- Scheduling Algorithms

- $\rightarrow$  RR, FP, EDF

- → Servers (SS, PollS., CBS, GRUB)

- □ Shared Resources

→ Priority Inheritance (MBWI wip...) Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

- Random Task Generators

- XML-based System Specification

- □ Qt-based GUI (optional)

- □ Open-source

- Platforms: Linux, Windows, Mac OS-X

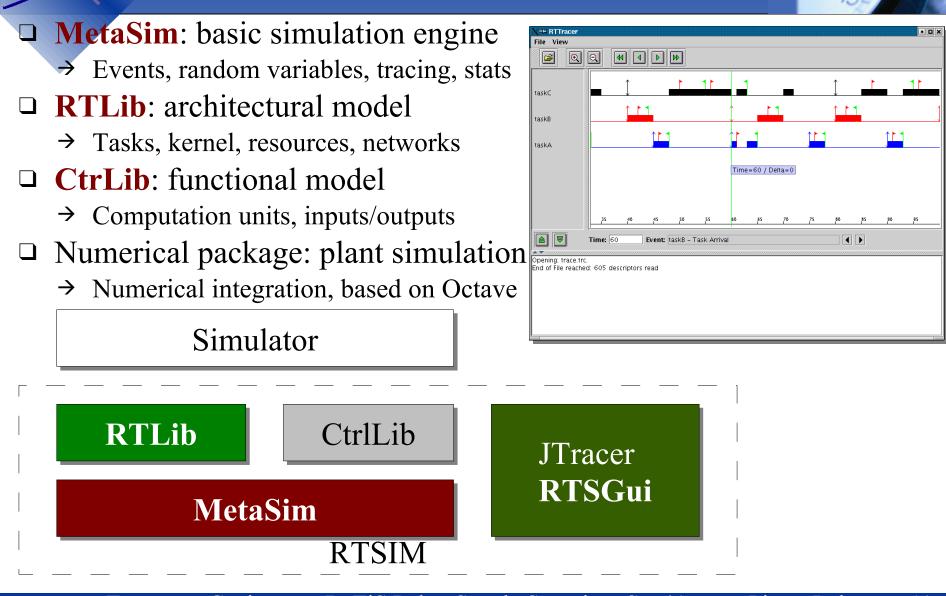

## **RTSIM Architecture**

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

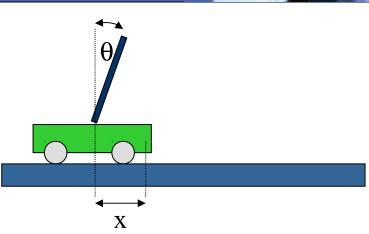

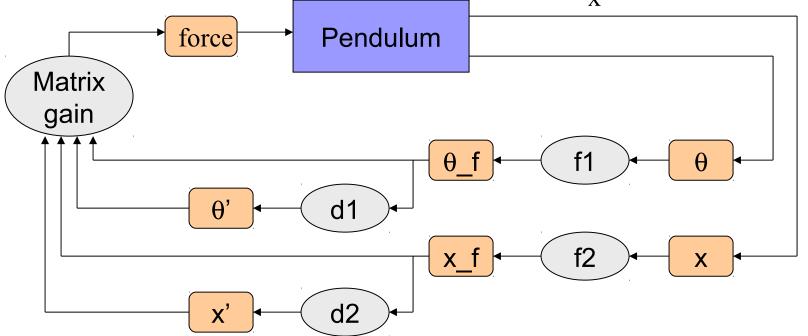

#### **RTSIM Example**

## **Inverted Pendulum**

- □ Two control loops: *angle* and *position*

- □ Video camera for sampling the *position*

- □ Potentiometer for sampling the *angle*

#### RTSIM Example Inverted Pendulum

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

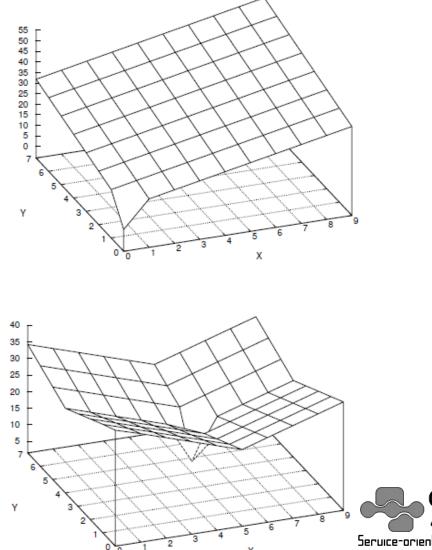

## **MCoreSim Features**

17

#### Simulates tile-based many-core systems

□ Based on OMNeT++

#### **Current features (extensible):**

- □ 2D Mesh and Torus

- □ Network Interface with flow-control for reliable comms

- Direction-Oriented Routing

- □ MMU accessing both Local Store and Remote Memory

#### Software stack as sequence of basic operations

- □ Load

- □ Store

- □ Core to core messages

- □ Internal core computations

#### **Outputs timing information (latency, throughput figures)**

## Why MCoreSim

#### **Other Multi-Core Simulators**

- □ COTSon

- → AMD SimNow

- 🗆 QEmu

- □ PhoenixSim

- □ NIRGAM & noxim (based on SystemC)

# No simulator covers future NoC with many cores and no shared memory or incoherent memory

#### **MCoreSim approach**

- □ Higher abstraction level (simulation performance benefits)

- □ Focus on impact of NoC on software performance (latency, throughput)

- Complements Clash for simulation purposes

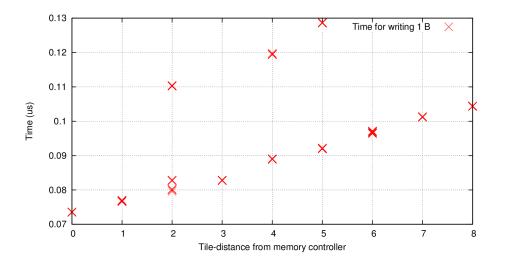

## **MCoreSim Example**

#### **Preliminary validation on the Intel SCC 48core, tile-based platform**

Service-oriented Operating Systems

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

# SCHED\_DEADLINE

21

#### **Features at a glance**

- □ New scheduling class for the Linux kernel

- Implements deadline-based resource reservations

- $\rightarrow$  grants scheduling guarantees to individual tasks

- Provides temporal isolation among tasks

- □ Model: budget, deadline, period

- □ Multiple variants (e.g., work-conserving)

## **ERIKA Enterprise RTOS**

**ENTERPRIS**

22

ERIKA

## **Performance and high efficiency**

- Advanced real-time scheduling algorithms

- □ RAM: Stack sharing to limit RAM consumption

- □ Flash: very low footprint (1-4 KB)

- **Portable API based on automotive standard** (OSEK/VDX)

- Supports a wide range of microcontrollers

- Including multicore systems

**Supported Microcontrollers**

23

# **Supported Microcontrollers**

- □ Microchip dsPIC

- □ Atmel AVR

- ARM7TDMI (Samsung KS32C50100, ST STA2051, UniBO MPARM)

- □ Tricore 2

- □ PPC e200 (MPC5674F (e200z7). MPC5668 (e200z6))

- □ Microchip PIC32

- □ Ensilica esiRISC

- □ Altera NIOS II (with multi-core support!)

- □ Lattice Mico32

**Development environment for Erika Enterprise Compliance with automotive standard** • OSEK OIL

- Schedulability analysis plugin

- **Template applications support**

- Easy development

- □ Multicore support

- □ Support for hardware debugging

- □ Based on the well-known Eclipse IDE

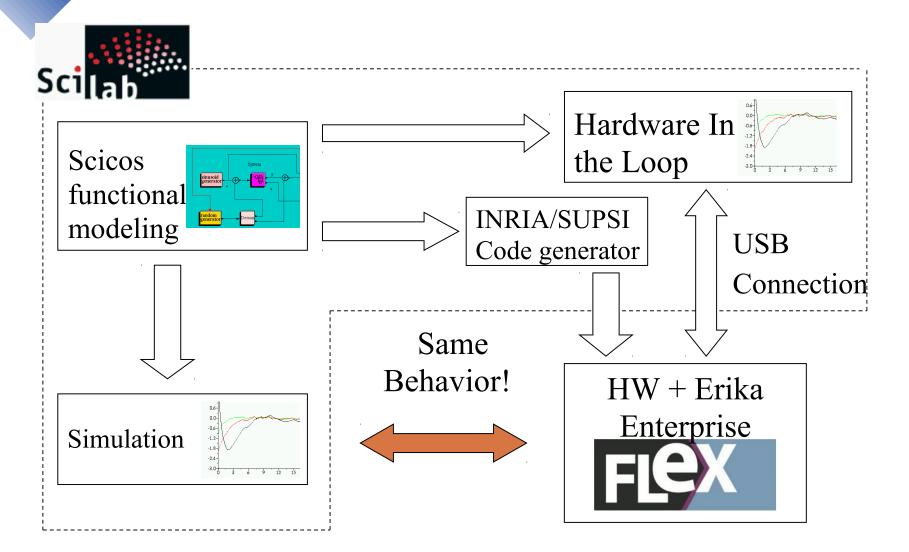

#### Fast Prototyping with Scilab/Scicos

in collaboration with INRIA (FR) and Supsi Lugano (CH)

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

26

# **ERIKA Enterprise License**

□ GPL + Linking Exception: possibility to statically link a proprietary application with the source code

→ http://en.wikipedia.org/wiki/GPL\_linking\_exception

## **RT-Druid IDE License**

□ Currently a demo license

□ Will be released soon under the EPL open-source license

## **Integration Efforts in the Automotive Domain**

#### Motivation: automotive systems sample requirements

# Several applications (an example is fuel injection control) are developed with the following characteristics:

- □ High cost-sensitiveness

- □ Faster CPU often not an option, limited availability of memory

- □ Large number of functional subsystems (~200) interacting exchanging several hundreds of communication signals

- System is multirate and characterized by tight timing constraints

- □ Utilization is very high (>90%) and mode changes are required

#### Model-based design using Simulink (SR) models Need to plan transition to AUTOSAR-based development

#### Motivation: automotive systems sample requirements

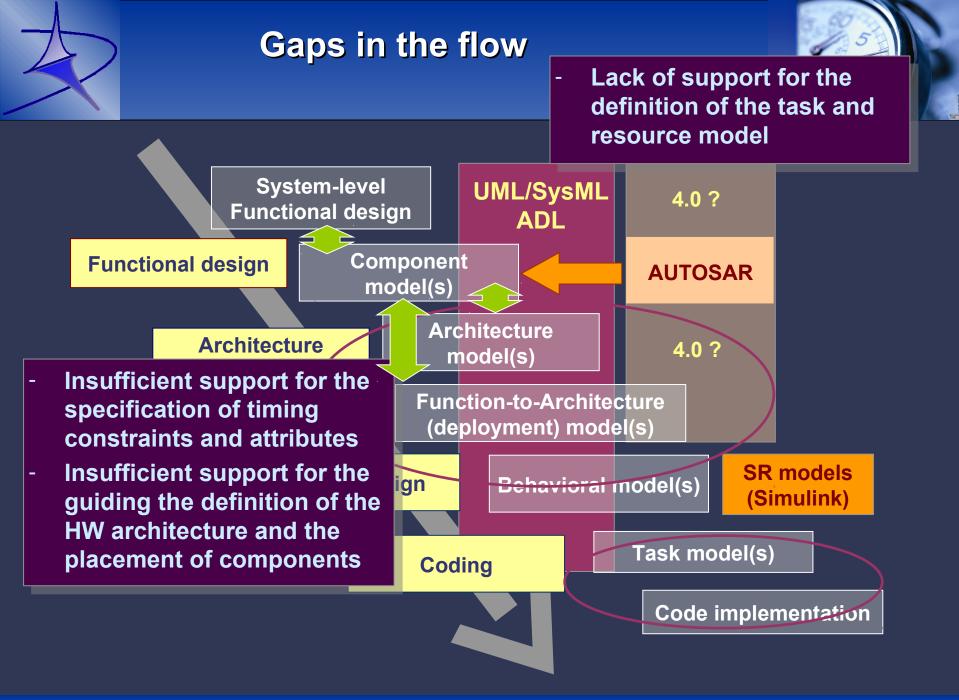

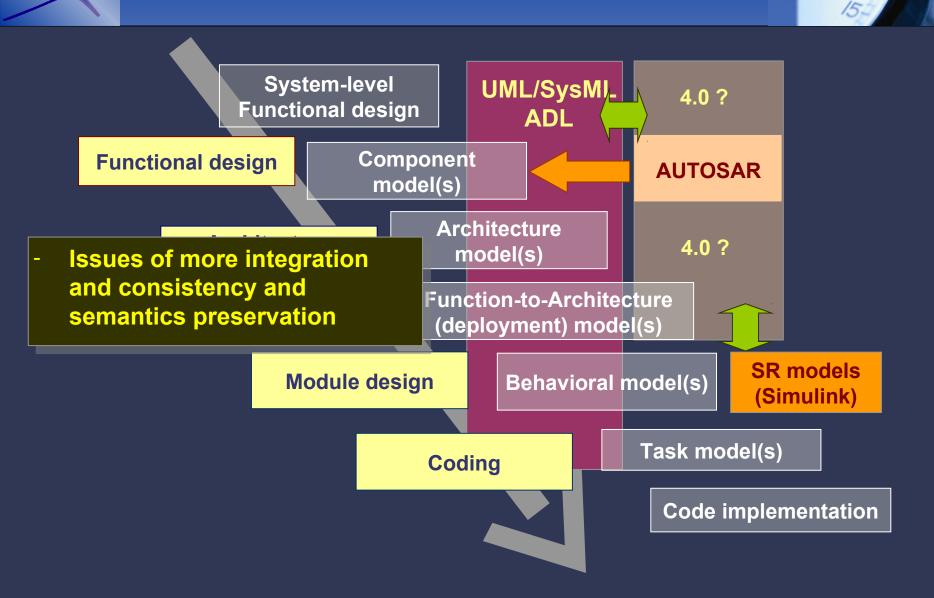

#### **Need** for

- Supporting the design of the task and resource model starting from system-level models to Simulink and AUTOSAR models

- → Enforce semantics preservation (partial orders, comm flows)

- → Optimize wrt performance metrics within timing constraints

- Algorithms that optimize memory use while enforcing deadlines

- $\rightarrow$  Use of preemption thresholds

- □ Model and control mode changes

#### Critical issues (just to mention a few)

- □ Lack of timing/behavior info in AUTOSAR models

- □ Lack of a formal timed event model

- □ Mapping of the functional model to the platform & task model

- → Mainly manual in the current practice Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

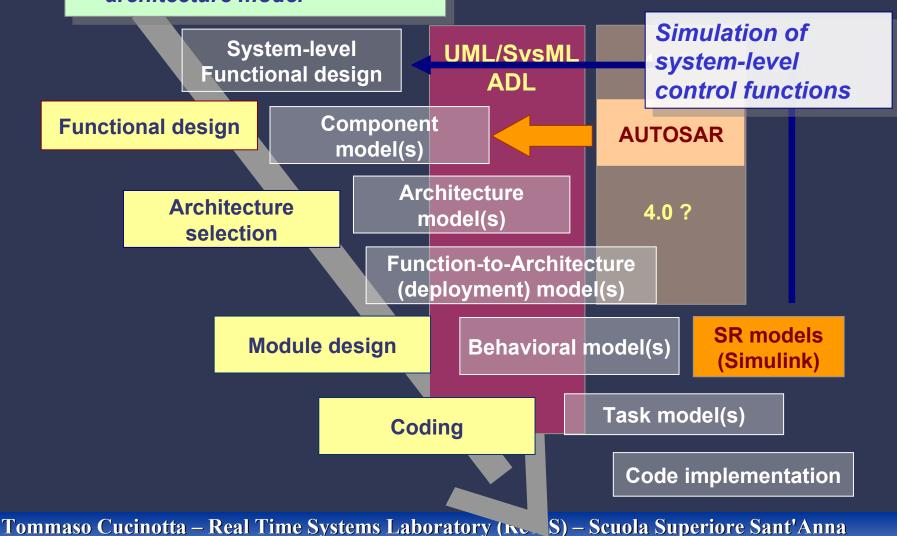

#### A Typical Flow: Heterogeneous Models

15

+ separation between the functional model and the architecture model

#### Frictions in the integration

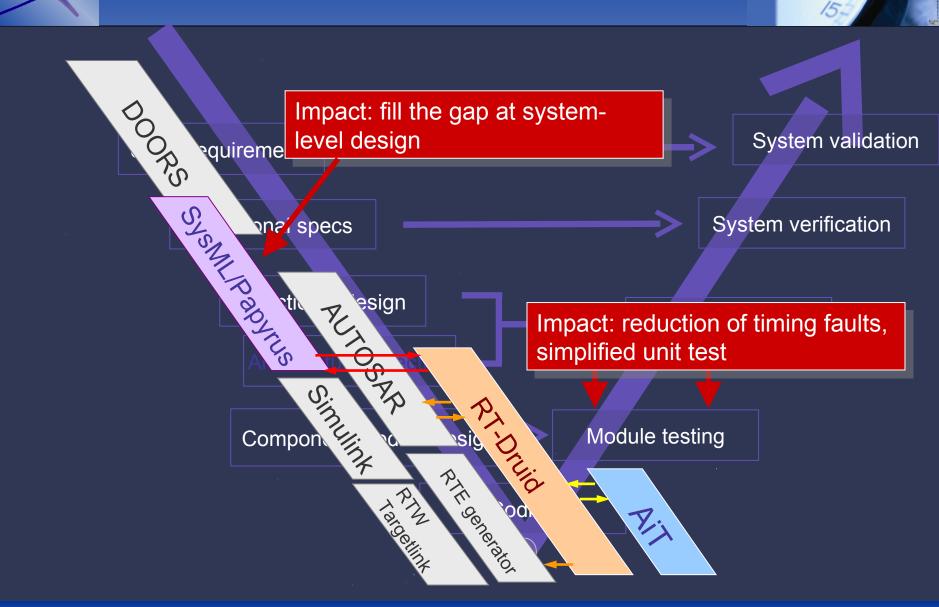

#### Heterogeneous Models in INTERESTED

**dSPACE** SystemDesk<sup>®</sup> SystemDesk is a tool from dSPACE for developing complex system architectures.

SystemDesk is able to **export AUTOSAR XML** files containing the system description for further analysis in RT-Druid.

Artop is an implementation of common base functionality for AUTOSAR development tools.

Artop can be used as an enhanced editor for preparing and validating **AUTOSAR XML** descriptions to be imported in RT-Druid.

AUTOSAR

XML

Papyrus is an integrated environment for graphical editing UML, SysML and MARTE.

Papyrus is able to **export RT-Druid RTD files** containing the system architecture.

RT-Druid

RTD

AUTOSAR XML

# RT)DRUID

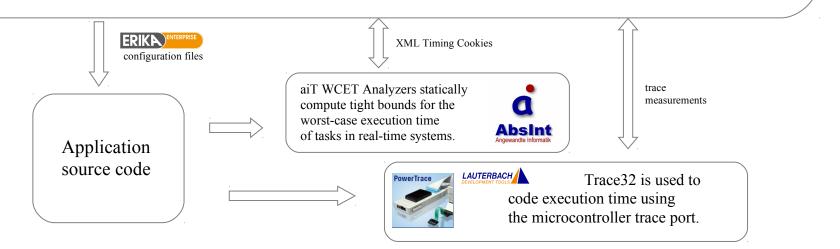

- import/export AUTOSAR XML files produced by SystemDesk and Artop;

- perform schedulability analysis;

- configure the ERIKA Enterprise RTOS based on the model using OSEK OIL or AUTOSAR XML;

- provide sensitivity analysis for understanding application timing bottlenecks;

- import timing annotations from AbsInt aiT using the XML Timing Cookies (XTC) standard;

- import timing annotations using trace measurements from Lauterbach Trace32.

## Conclusions

Tommaso Cucinotta – ReTiS Lab – Scuola Superiore Sant'Anna – Pisa – Italy

## Conclusions

36

#### **Tools and Standards for RTES Design and Development**

- □ Heterogeneous models, syntax and semantics

- $\rightarrow$  In particular, in the automotive domain

- □ Need for more integration & interoperability

- Issues partially addressed by the INTERESTED EU Project

#### **Related Resources**

**ReTiS** Website □ http://retis.sssup.it **RTSIM** Website □ http://rtsim.sssup.it/ **ARSim Website** □ http://home.gna.org/arsim/ **Evidence Website** □ http://www.evidence.eu.com/ **Erika Enterprise and RT-Druid Website** □ http://erika.tuxfamily.org/ **INTERESTED** Website □ http://www.interested-ip.eu/ **Automotive SPIN Italia** □ http://www.automotive-spin.it/index.php

## http://retis.sssup.it/people/tommaso